# A 1.86-kV double-layered NiO/β-Ga<sub>2</sub>O<sub>3</sub> vertical p-n heterojunction diode 🐵

Cite as: Appl. Phys. Lett. 117, 022104 (2020); https://doi.org/10.1063/5.0010052 Submitted: 06 April 2020 . Accepted: 28 June 2020 . Published Online: 14 July 2020

H. H. Gong, X. H. Chen 🕒, Y. Xu, F.-F. Ren, S. L. Gu, and J. D. Ye 📵

#### **COLLECTIONS**

Paper published as part of the special topic on Ultrawide Bandgap Semiconductors Note: This paper is part of the Special Topic on Ultrawide Bandgap Semiconductors.

This paper was selected as an Editor's Pick

# A 1.86-kV double-layered NiO/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub> vertical p-n heterojunction diode 📵

Cite as: Appl. Phys. Lett. 117, 022104 (2020); doi: 10.1063/5.0010052 Submitted: 6 April 2020 · Accepted: 28 June 2020 · Published Online: 14 July 2020

H. H. Gong, X. H. Chen, 1 Y. Xu, F.-F. Ren, 2 S. L. Gu, and J. D. Ye<sup>1,2,a)</sup>

#### **AFFILIATIONS**

School of Electronic Science and Engineering, Nanjing University, Nanjing 210023, China

Note: This paper is part of the Special Topic on Ultrawide Bandgap Semiconductors.

#### **ABSTRACT**

In this Letter, high-performance vertical NiO/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub> p-n heterojunction diodes without any electric field managements were reported. The devices show a low leakage current density and a high rectification ratio over  $10^{10}$  (at  $\pm 3$  V) even operated at temperature of 400 K, indicating their excellent thermal stability and operation capability at high temperature. Given a type-II band alignment of NiO/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub>, carrier transport is dominated by the interface recombination at forward bias, while the defect-mediated variable range hopping conduction is identified upon strong reverse electric field. By using the double-layer design of NiO with a reduced hole concentration of  $5.1 \times 10^{17}$  cm<sup>-3</sup>, the diode demonstrates an improved breakdown voltage ( $V_b$ ) of 1.86 kV and a specific on-resistance ( $R_{on,sp}$ ) of 10.6 m $\Omega$  cm $^2$ , whose power figure of merit  $(V_b^2/R_{on,sp})$  has reached 0.33 GW/cm<sup>2</sup>. The high breakdown voltage and low leakage current are outperforming other reported Ga<sub>2</sub>O<sub>3</sub> based p-n heterojunctions and Schottky barrier diodes without field plate and edge termination structures. TCAD simulation indicates that the improved  $V_{\rm b}$  is mainly attributed to the suppression of electric field crowding due to the decreased hole concentration in NiO. Such bipolar heterojunction is expected to be an alternative to increase the breakdown characteristics of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> power devices.

Published under license by AIP Publishing. https://doi.org/10.1063/5.0010052

β-Ga<sub>2</sub>O<sub>3</sub> is a promising ultra-wide bandgap semiconductor for high power device applications with a Baliga's figure of merit (FOM) superior to Si, SiC, and GaN materials. 1-3 Unipolar power devices, specifically Schottky barrier diodes (SBDs) based on β-Ga<sub>2</sub>O<sub>3</sub>, have been demonstrated in recent years. To achieve high breakdown voltages  $(V_b)$  and high figure-of-merits (FOMs), edge termination (ET) structures, such as Mg-ion implanted edge termination (ET), nitrogen-ion implanted guard ring field plate (FP), thermally oxidized termination, beveled mesa, and trench structure, have been implemented to suppress electric field crowding at the device edges.<sup>4–8</sup> For instance, fieldplated Ga<sub>2</sub>O<sub>3</sub> vertical trench SBDs have been realized with a V<sub>b</sub> value of 2.89 kV, which leads to a Baliga's FOM of 0.8 (0.95) GW/cm<sup>2</sup> under DC (pulsed) condition. Despite the remarkably performance improvement by various electrical field managements, the V<sub>b</sub> of Ga<sub>2</sub>O<sub>3</sub> SBD is mainly limited by the Fowler-Nordheim tunneling due to the relatively small Schottky barrier. Furthermore, the fabrication process for these ET structures is more complicated and costly. For instance, the imperfect edge termination and damages induced by associated etching and implantation processes inevitably lead to the  $V_b$ and FOM of present Ga<sub>2</sub>O<sub>3</sub> devices still far from the material limit.

Despite the rapid progress in the development of unipolar power devices, the difficulty in achieving p-type  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> remains an obstacle for the realization of advanced bipolar power devices that are more commonly used in practical applications.

An alternative strategy is to construct p-n heterojunctions by integrating n-type Ga<sub>2</sub>O<sub>3</sub> with other p-type semiconductors if the interface quality is controlled in a proper manner.  $^{10-12}$  To date,  $\beta\text{-}$ Ga<sub>2</sub>O<sub>3</sub> based p-n heterojunction diodes have been demonstrated, such as the  $\text{Cu}_2\text{O}/\beta\text{-Ga}_2\text{O}_3$  junction with a  $V_b$  of 1.49 kV and the NiO/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub> junction with a V<sub>b</sub> of 1.06 kV.<sup>11,12</sup> Among p-type oxide families, the wide-bandgap NiO material has promising potentials in the applications of diverse optoelectronic and power devices owing to its high visible spectral transparency and p-type conductivity stemming from nickel vacancies or monovalent impurities. 13-15 In this Letter, we constructed NiO/β-Ga<sub>2</sub>O<sub>3</sub> p-n heterojunction diodes by a doublelayer design of NiO with varied hole concentrations. By reducing the hole concentration from  $3.6 \times 10^{19}$  to  $5.1 \times 10^{17}$  cm<sup>-3</sup>, the leakage current density is reduced to 10<sup>-9</sup> A/cm<sup>2</sup> while a high rectification ratio over  $10^{10}$  (at  $\pm 3\,\mathrm{V}$ ) is still maintained even operated at a high temperature of 400 K. The resultant device has a record high  $V_{\rm b}$  of

<sup>&</sup>lt;sup>2</sup>Research Institute of Shenzhen, Nanjing University, Shenzhen 518000, China

<sup>&</sup>lt;sup>a)</sup>Author to whom correspondence should be addressed: yejd@nju.edu.cn

$1.86\,\mathrm{kV}$  compared with other  $\beta\text{-Ga}_2\mathrm{O}_3$  based p-n heterojunction diodes  $^{11,12}$  and yields a Baliga's FOM of  $0.33\,\mathrm{GW/cm}^2$ . Correlation of carrier transport mechanisms and device performance will be discussed.

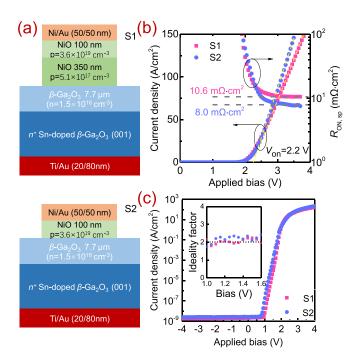

Figure 1(a) shows the cross section schematic of the vertical NiO/ β-Ga<sub>2</sub>O<sub>3</sub> heterojunction diodes. The 7.7-μm-thick Si-doped β-Ga<sub>2</sub>O<sub>3</sub> drift layers were purchased from Tamura Corporation, Japan, which were grown by halide vapor phase epitaxy (HVPE) on the high conductive Sn-doped (001)  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>. The electron concentration and mobility of the drift layer are  $1.5 \times 10^{16}$  cm<sup>-3</sup> and 130 cm<sup>2</sup>/V s, respectively, determined by Hall measurement at room temperature. The fabrication of p-n diode began with a full area back Ohmic contact of Ti/Au (20/80 nm) deposited by electron beam evaporation (EBE), followed by rapid thermal annealing at 470 °C for 1 min under N<sub>2</sub> ambient. Subsequently, the NiO layer was deposited by the radio frequency (RF) magnetron sputtering technique at room temperature on the β-Ga<sub>2</sub>O<sub>3</sub> drift layer, which was patterned into circular shape with a diameter of 200 µm. A Ni/Au (50/50 nm) metal stack was directly deposited upon the NiO layer by EBE to make an Ohmic contact, followed by the lift-off process. The RF power was 150 W, and the target was high purity (99.99%) NiO ceramics. The growth pressure was 0.6 Pa in an Ar/O2 mixed ambient. The flux ratios of Ar/O2 were tuned from 20:1 to 2:1 to modulate hole concentration. The device (denoted as S1) contains a double-layer of p-type NiO films, which is composed of a 350-nm-thick lower-side layer and a 100-nm-thick upper-side layer with their hole concentrations and mobility of  $5.1 \times 10^{17} \,\mathrm{cm}^{-3}$ ,  $0.94 \,\mathrm{cm}^2/\mathrm{V}\,\mathrm{s}$  and  $3.6 \times 10^{19} \,\mathrm{cm}^{-3}$ ,  $0.12 \,\mathrm{cm}^2/\mathrm{V}\,\mathrm{s}$ ,

**FIG. 1.** (a) Cross-section schematic of vertical NiO/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub> heterojunction diodes with two structural designs; (b) linear plots of J-V characteristics and extracted  $R_{\text{on,sp}}$  vs forward bias, the turn-on voltage is obtained by fitting the linear segment; and (c) semi-logarithmic plots of the J-V characteristics. The inset of (c) illustrates the extracted ideality factor.

respectively, obtained by Hall measurement at room temperature. To evaluate the electric and optical properties of the sputtered NiO, the NiO layer was also deposited on a sapphire substrate in the identical deposition condition as in the device fabrication process. The device S2 is only composed of a single p-NiO layer identical to the upper-side NiO layer in the device S1. The low-biased current-voltage (I-V) and capacitance-voltage (C-V) characteristics were measured by using a Keithley 2634B current source meter and an E4980A LCR meter, respectively. The high-biased I-V measurements were carried out by a Keithley 2657A current source meter at room temperature in Fluorinert.

Figure 1(b) shows the linear-scaled forward *J*–*V* and the extracted differential specific on-resistance (Ron,sp-V) characteristics of the diodes with an anode radius of 100  $\mu$ m. The  $R_{\rm on,sp}$  of devices S1 and S2 is extracted to be 10.6 and 8.0 m $\Omega$  cm<sup>2</sup>, respectively, both of which are larger than the reported values of most SBDs. It is mainly attributed to the large bulk resistance of a lightly doped p-NiO layer and Ohmic contact resistance between a Ni and NiO layer. The linear fitting in the forward biased  $I\!-\!V$  region yields the turn-on voltage ( $V_{\rm ON}$ ) of both devices S1 and S2 to be about 2.2 V, which is larger than the Schottky barrier height (SBH) of most Ga<sub>2</sub>O<sub>3</sub>-based SBDs. It is expected that  $V_{ON}$  for the p-n heterojunction is mainly determined by the energy difference of Fermi levels in the respective n- and p-type materials, which is approaching the bandgap of the constructed narrow bandgap material. Figure 1(c) depicts the semi-log J-V characteristics and high rectification ratios over  $10^{10}$  (at  $\pm 3$  V) are obtained for both devices. The ideality factors  $(\eta)$  in the inset of Fig. 1(c) are extracted with average values of about 2, which is a typical sign of the dominant interface recombination and will be discussed later.<sup>1</sup>

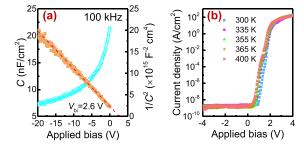

Figure 2(a) shows the C-V and  $1/C^2-V$  plots of the device S1 measured under 100 kHz. The capacitance of a p-n heterojunction diode is given by<sup>17</sup>

$$C = \left[ \frac{q\varepsilon_n \varepsilon_p \varepsilon_0 N_D N_A}{2(\varepsilon_n N_D + \varepsilon_p N_A)} \right]^{1/2} (V_{bi} - V_A)^{-1/2}, \tag{1}$$

where  $N_{\rm D}$  and  $N_{\rm A}$  are the donor and acceptor concentrations in the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> and NiO layer, respectively,  $\varepsilon_{\rm n}$  and  $\varepsilon_{\rm p}$  are the relative dielectric constants of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> and NiO with their respective values of 10 and 9.1; <sup>18,19</sup> And  $\varepsilon_{\rm 0}$ , q,  $V_{\rm bi}$ , and  $V_{\rm A}$  are the permittivity of vacuum, electronic charge, built-in potential, and applied voltage, respectively. The  $V_{\rm bi}$  was determined to be 2.6 V from the extrapolation to  $1/C^2=0$ , which is a bit larger than the  $V_{\rm ON}$  of 2.2 V derived from the I-V curves.

**FIG. 2.** (a) C-V and  $1/C^2-V$  characteristics measured at 100 kHz and (b) temperature dependent J-V characteristics from 300 to 400 K for device S1.

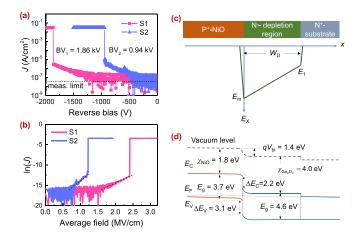

It may be resulted from the barrier height inhomogeneity across the large anode area. Assuming that all donors and acceptors are completely ionized, we estimated the electron concentration in  $\beta$ - $Ga_2O_3$  substrate to be  $1.6 \times 10^{16}$  cm<sup>-3</sup> based on the slop of  $1/C^2-V$ plot and a hole concentration of  $5.1 \times 10^{17}$  cm<sup>-3</sup> in the NiO layer. This estimated electron concentration is in good agreement with Hall carrier concentration. Figure 3(d) shows the schematic energy band diagram of NiO/β-Ga<sub>2</sub>O<sub>3</sub> p-n heterojunction at the condition of thermal equilibrium. In terms of the Anderson's model, the conduction band offset  $(\Delta E_{\rm C})$  at the interface can be theoretically determined to be 2.2 eV based on the energy difference in electron affinities ( $\chi_{\rm n}=4.0~{\rm eV}$  for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> and  $\chi_p = 1.8$  eV for NiO). Given the bandgaps of  $E_g^{\text{NiO}} = 3.7$  eV and  $E_g^{\text{Ga}_2\text{O}_3} = 4.6$  eV, the valence band offset ( $\Delta E_V$ ) is determined to be  $3.1 \,\mathrm{eV}$ , and the theoretical built-in potential  $(V'_{\mathrm{bi}})$  is 1.4 V. 11 Thus, the electron potential barrier in the conduction band for injecting electrons from  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> into NiO is  $V_a = (V'_{bi} + \Delta E_C)/q$ = 3.6 V, which almost equals to the NiO bandgap. However, the derived  $V_{\rm a}$  is much larger than  $V_{\rm ON}$  determined from  $I\!-\!V$  characteristics. The fact that an abnormal small "turn-on" voltage is inconsistent with the electron potential  $V_a$  has been also reported in several other reported wide-bandgap p-n heterojunctions. 10-12 It suggests that the defect-assisted tunneling and interface recombination could be dominant at the small forward bias regime. Indeed, due to the large lattice mismatch or intermixing problem, defective states will be formed and localized at the NiO and  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> interface, which will provide a pathway for electrons from the conduction band of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> injecting into valence band of NiO and recombining with holes there. 11,16,17 To evaluate the device thermal stability, temperature-dependent J-V characteristics of device S1 were shown in Fig. 2(b). The slight reduction of  $V_{\rm ON}$  with elevated ambient temperature ( $T_{\rm amb}$ ) from 300 to 400 K is resulted from the increased intrinsic carrier concentration, the shrinkage of bandgap energy, and the increased effective density of states at high temperature.<sup>22</sup> A surprising feature is that the reverse saturation current density remains very low at a level of less than 10<sup>-9</sup> A/cm<sup>2</sup>, and a rectification ratio over  $10^{10}$  (at  $\pm 3$  V) is maintained even at  $T_{\rm amb}$ of 400 K. The negligible dependence of leakage current and rectification

FIG. 3. (a) Comparison of breakdown characteristics for devices S1 and S2. (b) The plot of In (J) vs the average electric field. (c) Vertical electric field distribution of a punch-through p-n heterojunction. (d) Schematic energy band diagram of NiO/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub> p-n heterojunction at the condition of thermal equilibrium.

ratio on  $T_{\rm amb}$  suggests the devices have excellent thermal stability and operation performance at high-temperature.

The breakdown characteristics of devices in Fig. 3(a) show that, for both devices, the reverse leakage current remains almost unchanged in a measurement-limited level until reverse biases reach the breakdown points. The  $V_{\rm b}$  values for devices S1 and S2 are 1.86 and 0.94 kV, respectively. Specially for the device S1, the  $V_b$  is higher than that of the reported  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> SBDs without electric field managements, <sup>28–30</sup> and a FOM is yielded to be 0.33 GW/cm<sup>2</sup>. To identify the specific leakage mechanism, correlation between leakage current and electric field was investigated. Figure 3(b) illustrates ln(I) as a function of the average electric field  $E_{AV}$ , which is calculated by the applied reverse bias over the depletion layer thickness. For E < 0.5 MV/cm for S2 and E < 1.5 MV/cm for S1, the leakage current is almost unchanged due to the measurement limit. For both devices, at higher electric field before breakdown point, the leakage current increases steeper with  $E_{\rm AV}$ . Similar to the transport mechanism in GaN vertical p-n diodes, the observed  $ln(J) \propto E_{AV}$  linearity is a sign of the dominant variable range hopping (VRH) conduction inside the depletion region.<sup>23–25</sup> There exists a model of charge transfer in NiO material, which proposes that charge carriers hop over potential barriers between defect sites, the height of the barriers being correlated with the intersite separation.<sup>26</sup> During the growth of NiO, higher oxygen partial pressure leads to the improved oxygen incorporation and hole concentration in the NiO film. In this case, more Ni vacancies are formed with increased lattice distortion around the Ni3+ sites; thus, carriers are more likely to hop between additional defect sites.

Besides the hopping conduction, electric field distribution also plays a critical role in the breakdown performance. The vertical electric field distribution of the punch-through p-n heterojunction is shown in Fig. 3(c), which exhibits that the 7.7- $\mu$ m drift layer of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> has been depleted completely under the breakdown voltage.<sup>27</sup> The potential drops at p-NiO layer and N<sup>+</sup>-β-Ga<sub>2</sub>O<sub>3</sub> substrate are negligible due to their relatively higher carrier concentration as compared with the β-Ga<sub>2</sub>O<sub>3</sub> drift layer. The electric field at the interface between the drift region and the  $N^+$  end region and the  $V_b$  supported by the punchthrough diode are given by<sup>2</sup>

$$E_1 = E_{\text{max}} - \frac{q N_{\text{D}} W_{\text{D}}}{\varepsilon_{\text{U}} \varepsilon_{\text{O}}},\tag{2}$$

$$E_{1} = E_{\text{max}} - \frac{qN_{\text{D}}W_{\text{D}}}{\varepsilon_{\text{n}}\varepsilon_{0}},$$

$$V_{\text{b}} = E_{\text{AV}}W_{\text{D}} = \left(\frac{E_{\text{max}} + E_{1}}{2}\right)W_{D},$$

(2)

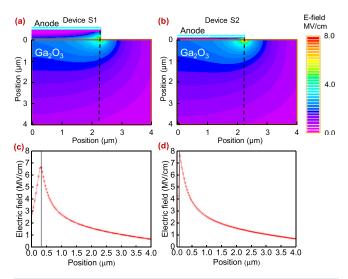

where  $E_{\rm max}$  is the maximum electric field at the p-n junction interface,  $N_{\rm D}$  is the doping concentration in the  $N^-$  drift region,  $W_{\rm D}$  is the width of the drift region, and  $E_1$  is the electric field at the interface between  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> drift region and substrate. Based on Eqs. (2) and (3),  $E_{\text{max}}$ and  $E_1$  are calculated to be 3.5 MV/cm and 1.4 MV/cm for device S1, and 2.4 MV/cm and 0.18 MV/cm for device S2, respectively. The improved V<sub>b</sub> in device S1 with double-layered NiO is a result of the suppression of the electric field crowding at the device edge. Figures 4(a) and 4(b) show two-dimensional electric field distribution at a reverse bias of 0.94 kV for devices S1 and S2, respectively, using Silvaco TCAD software. Electric field profiles along the cutline at the device edge have been extracted and shown in Figs. 4(c) and 4(d). The peak electric field of devise S1 and S2 reaches the value of 6.7 and 7.8 MV/cm, respectively. The magnitude of the peak electric field for

**FIG. 4.** Two-dimensional electric field distributions at a reverse bias of 0.94 kV of (a) device S1 and (b) S2 simulated by Silvaco TCAD software. Extracted electric field profiles along the cutline at the device edges of (c) device S1 and (d) S2.

device S2 has almost reached the theoretical Ga<sub>2</sub>O<sub>3</sub> breakdown electric field (8 MV/cm). In comparison, with decreased hole concentration, the depletion layer in the p-NiO layer becomes wider and the electric field spreads into the NiO layer rather than converging to the device edge at the Ga<sub>2</sub>O<sub>3</sub> region. Consequently, the point where electric field crowding occurs moves from device edge to the inside, which results in suppression of the electric field crowding at the device edge. The improved breakdown performance and the suppressed electric field crowding by decreasing hole concentration has been also exhibited in the beveled-mesa GaN vertical p-n diodes.<sup>28</sup>

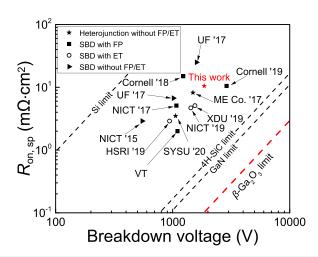

Figure 5 benchmarks the  $R_{\text{on,sp}}$  vs  $V_b$  plot of the state-of-the-art p-n heterojunction diodes and SBDs based on  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>. As marked,

**FIG. 5.** Benchmark of  $R_{\text{on,sp}}$  vs  $V_{\text{b}}$  of state-of-the-art heterojunction p—n diodes and SBDs based on  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>, including heterojunction diodes, <sup>11,12</sup> SBDs with FP, <sup>7,8,32,33</sup> SBDs with ET, <sup>4-6</sup> SBDs without FP/ET. <sup>29–31</sup> The red star represents this work.

the  $V_{\rm b}$  of the device developed here is highest compared with that of other heterojunction p–n diodes <sup>11,12</sup> and is also outperforming that of the best SBDs without FP and ET structures reported to date. <sup>29–31</sup> It is noted that the reported  $E_{\rm max}$  of 3.5 MV/cm herein is larger than that of most SiC and GaN devices, but it is still much lower than the theoretical breakdown field of Ga<sub>2</sub>O<sub>3</sub> material (8 MV/cm). It may be also limited by the breakdown field of NiO material, which is relatively defective and has a low energy bandgap. Therefore, aside from the implementation of field plate and edge termination structures, the improvement of NiO material and interface quality is necessary to further improve the breakdown field.

In summary, high-performance vertical NiO/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub> p–n heterojunction diodes without any electric field managements have been demonstrated. By adopting a double-layer design of NiO with a reduced hole concentration, the resultant device has a low leakage current and a rectification ratio over 10<sup>10</sup> (at  $\pm 3$  V) is maintained even at 400 K. The breakdown voltage of device reaches 1.86 kV, which is the record-high value among Ga<sub>2</sub>O<sub>3</sub> p–n heterojunction diodes and SBDs without FP and edge ET structures. The improved breakdown voltage is attributed to the suppression of electric field crowding by decreasing hole concentration in NiO. Together with its excellent thermal stability, such a type-II bipolar heterojunction is an alternative for developing high performance  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> power rectifiers operating at high temperatures.

This work was supported by the National Key R&D Program (No. 2018YFB0406502), the State Key R&D project of Jiangsu (Nos. BE2018115 and BE2019103), the State Key R&D project of Guangdong (No. 2020B010174002), the National Natural Science Foundation of China (Nos. 61774081 and 91850112), and Shenzhen Fundamental Research Project (Nos. JCYJ 20170818110619334, JCYJ 20180307154632609, and JCYJ20180307163240991).

## DATA AVAILABILITY

The data that support the findings of this study are available within the article.

### **REFERENCES**

<sup>1</sup>M. Higashiwaki, K. Sasaki, A. Kuramata, T. Masui, and S. Yamakoshi, Appl. Phys. Lett. 100, 013504 (2012).

<sup>2</sup>S. J. Pearton, J. C. Yang, P. H. Cary, F. Ren, J. Kim, M. J. Tadjer, and M. A. Mastro, Appl. Phys. Rev. 5, 011301 (2018).

J. Pearton, F. Ren, M. Tadjer, and J. Kim, J. Appl. Phys. 124, 220901 (2018).

H. Zhou, Q. L. Yan, J. C. Zhang, Y. J. Lv, Z. H. Liu, Y. N. Zhang, K. Dang, P. F. Dong, Z. Q. Feng, Q. Feng, J. Ning, C. F. Zhang, P. J. Ma, and Y. Hao, IEEE Electron Device Lett. 40, 1788 (2019).

<sup>5</sup>C. H. Lin, Y. Yuda, M. H. Wong, M. Sato, N. Takekawa, K. Konishi, T. Watahiki, M. Yamamuka, H. Murakami, Y. Kumagai, and M. Higashiwaki, IEEE Electron Device Lett. **40**, 1487 (2019).

<sup>6</sup>Y. G. Wang, Y. J. Lv, S. B. Long, X. Y. Zhou, X. B. Song, S. L. Liang, T. T. Han, X. Tan, Z. H. Feng, S. J. Cai, and M. Liu, IEEE Electron Device Lett. 41, 131 (2020).

<sup>7</sup>N. Allen, M. Xiao, X. D. Yan, K. Sasaki, M. J. Tadjer, J. H. Ma, R. Z. Zhang, H. Wang, and Y. H. Zhang, IEEE Electron Device Lett. 40, 1399 (2019).

<sup>8</sup>W. S. Li, K. Nomoto, Z. Y. Hu, D. Jena, and H. L. G. Xing, IEEE Electron Device Lett. 41, 107 (2020).

<sup>9</sup>A. Kyrtsos, M. Matsubara, and E. Bellotti, Appl. Phys. Lett. 112, 032108 (2018).

Y. Kokubun, S. Kubo, and S. Nakagomi, Appl. Phys. Express 9, 091101 (2016).

X. Lu, X. D. Zhou, H. X. Jiang, K. W. Ng, Z. M. Chen, Y. L. Pei, K. M. Lau, and G. Wang, IEEE Electron Device Lett. 41, 449 (2020).

- <sup>12</sup>T. Watahiki, Y. Yuda, A. Furukawa, M. Yamamuka, Y. Takiguchi, and S. Miyajima, Appl. Phys. Lett. 111, 222104 (2017).

- <sup>13</sup> F. Vera, R. Schrebler, E. Muñoz, C. Suarez, P. Cury, H. Gómez, R. Córdova, R. E. Marotti, and E. A. Dalchiele, Thin Solid Films 490, 182 (2005).

- <sup>14</sup>Y. M. Lu, W. S. Hwang, and J. S. Yang, Surf. Coat. Technol. 155, 231 (2002).

- <sup>15</sup>M. Tyagi, M. Tomar, and V. Gupta, IEEE Electron Device Lett. **34**, 81 (2013).

- <sup>16</sup>M. Grundmann, R. Karsthof, and H. von Wenckstern, ACS Appl. Mater. Interfaces 6, 14785 (2014).

- <sup>17</sup>J. P. Donnelly and A. G. Milnes, IEEE Trans. Electron Devices 14, 63 (1967).

- <sup>18</sup>M. Passlack, E. F. Schubert, W. S. Hobson, M. Hong, N. Moriya, S. N. G. Chu, K. Konstadinidis, J. P. Mannaerts, M. L. Schnoes, and G. J. Zydzik, J. Appl. Phys. 77, 686 (1995).

- <sup>19</sup>K. V. Rao and A. Smakula, J. Appl. Phys. **36**, 2031 (1965).

- <sup>20</sup>M. Mohamed, K. Irmscher, C. Janowitz, Z. Galazka, R. Manzke, and R. Fornari, Appl. Phys. Lett. 101, 132106 (2012).

- <sup>21</sup>D. Kawade, S. F. Chichibu, and M. Sugiyama, J. Appl. Phys. **116**, 163108 (2014).

- <sup>22</sup>Y. Xi and E. F. Schubert, Appl. Phys. Lett. **85**, 2163 (2004).

- <sup>23</sup>Y. Zhang, H. Y. Wong, M. Sun, S. Joglekar, L. Yu, N. A. Braga, R. V. Mickevicius, and T. Palacios, in IEDM Technical Digest (2015), pp. 35.1.1–35.1.4.

- <sup>24</sup>D. P. Han, C. H. Oh, H. Kim, J. I. Shim, K. S. Kim, and D. S. Shin, IEEE Trans. Electron Devices 62, 587 (2015).

- 25Z. Y. Hu, K. Nomoto, M. Qi, W. S. Li, M. D. Zhu, X. Gao, D. Jena, and H. L. G. Xing, IEEE Electron Device Lett. 38, 1071 (2017).

- <sup>26</sup>P. Lunkenheimer, A. Loidl, C. R. Ottermann, and K. Bange, Phys. Rev. B 44, 5927 (1991).

- <sup>27</sup>B. J. Baliga, in Fundamentals of Power Semiconductor Devices (Springer, Raleigh, NC, 2019), Chap. 3, pp. 100–102.

- <sup>28</sup>T. Maeda, T. Narita, H. Ueda, M. Kanechika, T. Uesugi, T. Kachi, T. Kimoto, M. Horita, and J. Suda, IEEE Electron Device Lett. 40, 941 (2019).

- <sup>29</sup>J. C. Yang, S. Ahn, F. Ren, S. J. Pearton, S. Jang, and A. Kuramata, IEEE Electron Device Lett. 38, 906 (2017).

- <sup>30</sup>J. C. Yang, S. Ahn, F. Ren, S. J. Pearton, S. Jang, J. Kim, and A. Kuramata, Appl. Phys. Lett. **110**, 192101 (2017).

- 31 M. Higashiwaki, K. Sasaki, K. Goto, K. Nomura, Q. T. Thieu, R. Togashi, H. Murakami, Y. Kumagai, B. Monemar, A. Koukitu, A. Kuramata, and S. Yamakoshi, in Proceedings of 73rd IEEE Device Research Conference (2015), pp. 20–30.

- pp. 29–30.

32 K. Konishi, K. Goto, H. Murakami, Y. Kumagai, A. Kuramata, S. Yamakoshi, and M. Higashiwak, Appl. Phys. Lett. 110, 103506 (2017).

- <sup>33</sup>W. S. Li, Z. Y. Hu, K. Nomoto, Z. X. Zhang, J. Y. Hsu, Q. T. Thieu, K. Sasaki, A. Kuramata, D. Jena, and H. L. G. Xing, Appl. Phys. Lett. 113, 202101 (2018).