【国际论文】Nat.Commun.丨加利福尼亚大学——用于 β-Ga₂O₃ 薄膜晶体管的低温压力辅助液态金属印刷技术

日期:2025-02-25阅读:939

近期,由美国加利福尼亚大学圣迭戈分校的研究团队在学术期刊 Nature Communications 发布了一篇名为 Low-temperature pressure-assisted liquid-metal printing for β-Ga2O3 thin-film transistors(用于 β-Ga2O3 薄膜晶体管的低温压力辅助液态金属印刷技术)的文章。

通讯作者介绍

Kenji Nomura 教授的研究横跨材料科学和设备物理学领域。专长是开发宽带隙半导体和电子器件,开辟了基于非晶氧化物半导体的薄膜晶体管技术领域的研究。目前主要目标是为下一代可穿戴电子设备(如显示器和传感器应用)开发新型非晶氧化物半导体材料和高性能电子器件。领导研究小组对基于氧化物的先进纳米结构电子器件进行探究。研究小组基于理论和实验方法,致力于从材料设计、合成、薄膜生长到器件建模、制造和测试等多个方面的研究。他的研究目标是在新型材料开发的基础上进一步发展氧化物半导体器件技术。

背景

氧化物半导体(如β-Ga2O3)因宽禁带(4.4–4.9 eV)和高电子迁移率(100–200 cm2·V-1·s-1),在功率电子和柔性器件中潜力巨大。然而,传统制备方法(如物理气相沉积)需高温(>600°C)且成本高,限制了其应用。随着对可持续高性能电子设备和集成电路需求的不断增加,现有低温工艺(<200°C)的 β-Ga2O3 TFT迁移率低(<2 cm2·V-1·s-1),且需后处理退火。开发低温、真空无关的制造技术对推动柔性电子和可持续器件至关重要。因此,开发低温、无真空、非控制气氛的氧化物 TFT 制造工艺至关重要。

摘要

开发一种低温且成本效益高的制造工艺用于能效高、性能优异的氧化物薄膜晶体管(TFT),是推动下一代器件应用(如可穿戴和柔性电子产品)发展的关键步骤。在多种方法中,液态金属印刷技术被认为是一种有前景且成本效益高的氧化物半导体工艺,因其固有的优点,如无需真空、低热预算、高吞吐量和可扩展性。本研究开发了一种压力辅助液态金属印刷技术,实现了低温合成多晶宽带隙 n 型氧化物 TFT。基于约 3 nm 厚 β-Ga2O3 通道的 n 型氧化物 TFTs 展示了良好的 TFT 开关特性,阈值电压约为 3.8 V,饱和迁移率约为 11.7 cm2 V−1 s−1,开关电流比约为 109,亚阈值斜率约为 163 mV/decade。此外,我们还观察到在高压条件下制备的非化学计量 GaOx 通道表现出 p 型操作。为了向氧化物电路应用推进,团队开发了基于氧化物 TFT 的高性能反相器。

主要内容

研究团队提出了一种名为压力辅助液态金属印刷(PA-LMP)的技术,用于低温(150°C)合成高质量的多晶 β-Ga2O3 纳米片,并成功用于制造高性能的 β-Ga2O3 薄膜晶体管(TFT)。通过在液态金属表面施加外部压力,该技术促进了 Ga2O3 的结晶过程,直接在低温下生长出 β-Ga2O3 纳米片。基于该技术制造的 TFT 表现出优异的电气性能,包括饱和迁移率(11.7 cm2/V·s)、开/关电流比(约 109)和亚阈值斜率(163 mV/decade)。此外,在高压条件下制备的非化学计量 GaOx 通道中观察到了 p 型行为,并基于此开发了高性能的氧化物反相器电路。

实验细节

· 通过将高纯度镓(Ga)加热至 50°C 熔化,形成液态金属。将液态 Ga 滴放置在预热至所需工艺温度(80–200°C)的 SiO2/Si 衬底上,施加外部压力(29–206 kPa),促进氧化镓的结晶。

· 经过 3 分钟的挤压后,小心地将顶部衬底垂直分离,得到均匀的超薄 Ga2O3 纳米片。

· 使用 150 nm 厚的热氧化 SiO2/n⁺-Si 衬底作为栅极绝缘层和栅极电极。

· 通过光刻和化学湿法刻蚀定义通道区域。

· 使用脉冲激光沉积(PLD)沉积 40 nm 厚的 ITO 源漏电极。

· 所有电气特性在室温下使用半导体参数分析仪进行测量。TFT 设备展示出标准的 MOSFET 特性,具有高迁移率和低漏电流。

创新点

· PA-LMP 方法在 150°C 以下直接合成高质量的多晶 β-Ga2O3 纳米片,突破了传统高温工艺的限制。

· 通过外部压力优化氧化镓的结晶过程,提高了低温下氧化物半导体的电气性能。

· 在高压条件下制备的非化学计量 GaOx 通道中,成功观察到 p 型行为,并开发出基于此的反相器电路。

· 通过 TCAD 模拟分析了不同工艺条件下TFT性能的变化,发现主要来自亚带隙缺陷态密度的变化。

结论

1、研究总结:PA-LMP 技术成功在低温(150°C)下制备高性能 β-Ga2O3 TFT,并验证其在低功耗逆变器中的应用。

2、主要贡献:提出压力调控结晶的机制,为宽禁带氧化物半导体的低温制造提供了新思路。

3、未来方向:需深入探究压力对 β-Ga2O3 结晶的微观机制,优化 p 型 GaOx 性能,并拓展至复杂电路集成。

实验图示

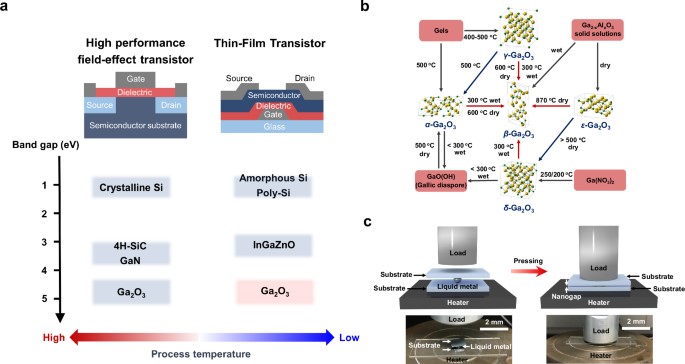

图1 | 用于 β-Ga2O3 薄膜晶体管(TFT)的压力辅助液态金属打印。a图展示了开发低温处理的宽禁带 Ga2O3 TFT 的动机和目的。b图展示了 Ga2O3 多态性的相变关系。c图展示了所开发的用于 Ga2O3 纳米片制备的压力辅助液态金属打印路线的示意图和照片。

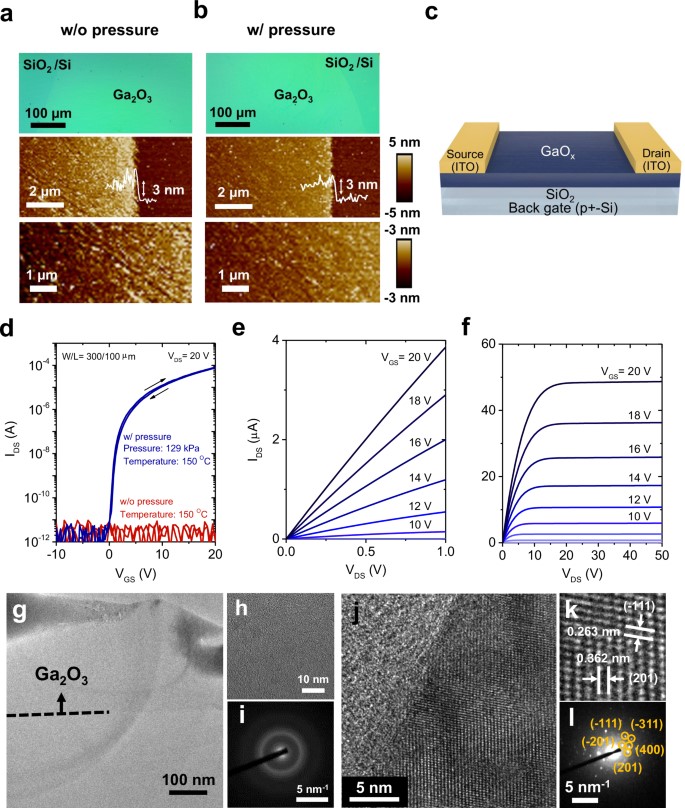

图2 | Ga2O3 薄膜的材料与电学性能表征。通过传统液态金属打印(LMP)(未施加打印工艺压力)和压力辅助液态金属打印(PA-LMP)(施加的打印工艺温度 Tp 为 150°C,打印工艺压力 Pp 为129 kPa)方法制备的 Ga2O3 纳米片的光学显微镜图像和原子力显微镜(AFM)图像(包括截面台阶高度轮廓)。c图为 GaOx 薄膜晶体管(TFT)的器件结构示意图。d图展示了通过LMP(Tp 为 150°C,Pp为 0 kgf/cm2)和PA-LMP(Tp 为 150°C,Pp 为 129 kPa)方法制备的 Ga2O3 TFT 的典型传输特性。(IDS:漏极电流,VDS:漏源电压,VGS:栅极偏置)TFT 的沟道宽度 W 和长度 L 分别为 300 μm 和 100 μm。e图为 Ga2O3 TFT 典型输出特性中线性区的放大视图。f图为 Ga2O3 TFT 的典型输出特性。g图为通过传统 LMP 路线(未施加打印工艺压力)合成的 Ga2O3 纳米片的低倍率高分辨率透射电子显微镜(HRTEM)图像。对应的h图为高倍率 HRTEM 图像,i图为选区电子衍射(SAED)图案。j图为通过压力辅助液态金属路线(Tp 为150°C,Pp 为 129 kPa)合成的 Ga2O3 纳米片的低倍率 HRTEM 图像。对应的k图为高倍率 HRTEM 图像,l图为 SAED 图案。

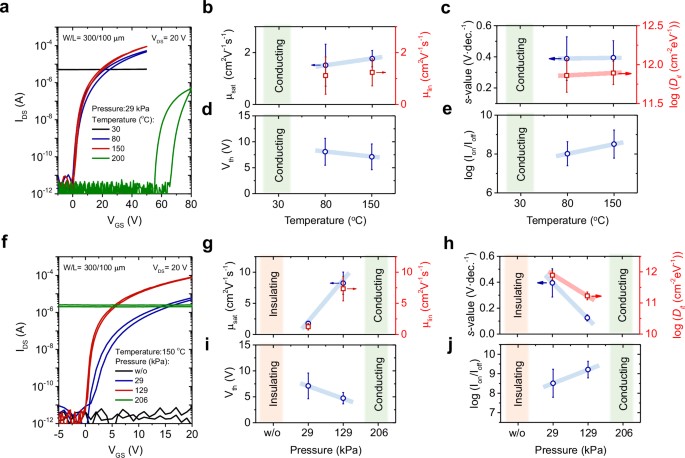

图3 | 打印工艺对 Ga2O3 薄膜晶体管(TFT)性能的影响。a图展示了在 29 kPa 的单轴工艺压力下,不同打印工艺温度下 Ga2O3 纳米片 TFT 的传输特性变化。对应的 TFT 参数包括b图的饱和迁移率(μsat)和线性迁移率(μlin),c图的亚阈值摆幅(s值)和陷阱态密度(Dit),d图的阈值电压(Vth),以及e图的开/关电流比。f图展示了在 150°C 的打印工艺温度下,不同工艺压力下 Ga₂O₃ TFT 的传输特性变化。对应的 TFT 参数包括g图的 μsat 和 μlin,h图的 s 值和 Dit,i图的 Vth,以及j图的开/关电流比。(误差条是根据不同样品中 16 个代表性工作器件的数据计算得出的。)

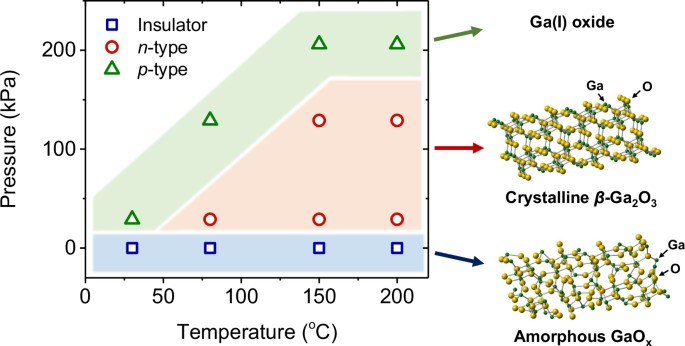

图4 | 液态金属打印生长的 Ga2O3 薄膜的电学性能。总结了在不同打印工艺条件(包括单向压力和温度)下,使用压力辅助液态金属路径生长的氧化镓纳米片通道的电学性能。

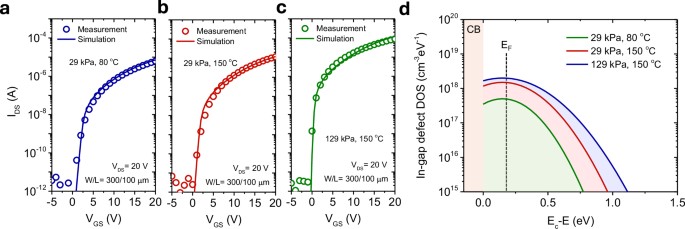

图5 | Ga2O3 薄膜晶体管(TFT)的 TCAD 模拟。不同打印工艺条件下Ga2O3 TFT在漏源电压 VDS=20V 时的测量(符号)和模拟(线条)传输曲线对比。(a)打印温度 Tp 为 80°C,打印压力 Pp 为 29 kPa;(b)打印温度 Tp 为 150°C,打印压力 Pp 为 29 kPa;(c)打印温度 Tp 为 150°C,打印压力 Pp 为 129 kPa。d图展示了不同打印工艺条件下 Ga2O3 纳米片通道的带隙内态密度(DOS)分布。费米能级(EF)位于Ec-EF=0.23 eV处。(Ec:导带边能量,CB:导带。)进行 TCAD 模拟以提取 Ga2O3 TFT 中的带隙缺陷 DOS 分布。通过仅使用高斯分布优化受主类缺陷(电子陷阱态),可以准确模拟测量的 I-V 曲线,高斯分布表示为 gG(E) = NGD × exp[-(Ec-EGA)^2 / (2×WGD^2)],其中 NGD 是高斯分布中心能量 EGA 处的态密度,Ec 是参考零点的导带边能量,EGA 是gG(E)的中心能量,WGD 是特征衰减能量。

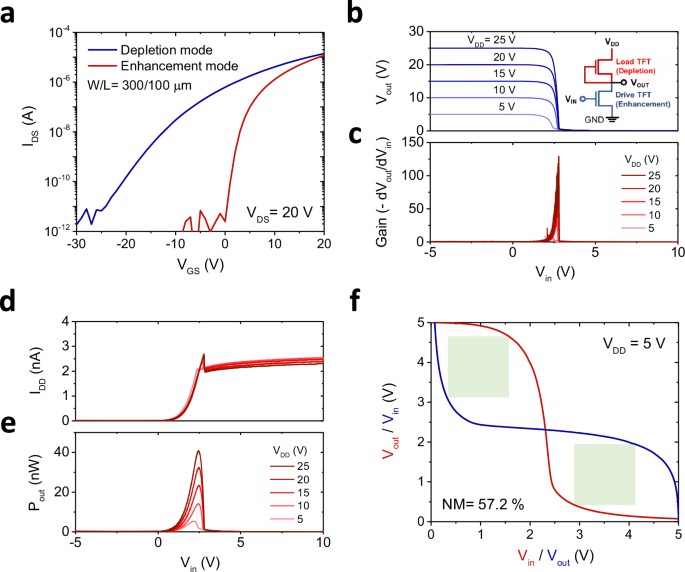

图6 | 基于 Ga2O3 晶体管的 N 型金属氧化物半导体(NMOS)反相器。NMOS 反相器是一种使用 N 型金属氧化物半导体场效应晶体管(NMOS 晶体管)和上拉电阻或负载晶体管构建的逻辑电路。a图展示了耗尽型和增强型 Ga2O3 薄膜晶体管(TFT)的典型传输特性。(用于 NMOS 电路演示的 Ga2O3 纳米片是在生长温度为 150°C、生长压力为 29 kPa 的条件下生长的。耗尽型 TFT 是通过在 100°C 的真空条件下进行后退火处理而制成的。)b图为基于 Ga2O3 TFT 的 NMOS 反相器的电压传输特性(VTC)。c图为基于 Ga2O3 TFT 的 NMOS 反相器对应的电压增益。插图:由增强型/耗尽型 Ga2O3 TFT组成的零栅源电压(VGS)负载 NMOS 反相器的电路示意图。d图为对应的供电电流(IDD)。e图为基于 Ga2O3 TFT的 NMOS 反相器的输出功率消耗(Pout)。f图为基于 Ga2O3 TFT 的 NMOS 反相器的噪声容限(NM)的蝶形曲线。(Vin:输入电压,Vout:输出电压,VDD:供电电压)。

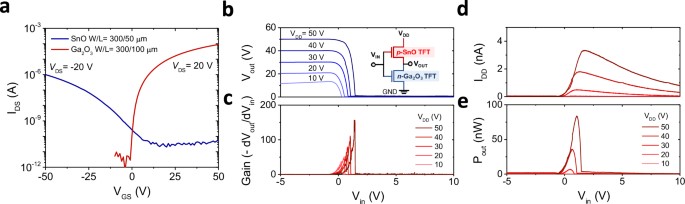

图7 | 基于 N 型 Ga2O3 / P 型 SnO 晶体管的互补金属氧化物半导体(CMOS)反相器。CMOS 反相器是一种逻辑电路,由一个 P 型金属氧化物半导体场效应晶体管(PMOS)作为上拉器件和一个 N 型金属氧化物半导体场效应晶体管(NMOS)作为下拉器件组成。a图展示了在漏源电压 VDS 为-20V 时的超薄 P 型 SnO 薄膜晶体管(TFT)和漏源电压 VDS 为 20V 时的 N 型 Ga2O3 薄膜晶体管的典型传输特性。(用于 CMOS 电路演示的 Ga2O3 纳米片是在生长温度为150°C、生长压力为 29 kPa 的条件下生长的。)b图为电压传输特性(VTC)。c图为基于 P 型 SnO / N 型 Ga2O3 TFT 的 CMOS 反相器对应的电压增益。插图:基于相应氧化物 TFT 的 CMOS 反相器电路示意图。d图为对应的供电电流(IDD)。e图为基于 P 型 SnO / N 型 Ga2O3 TFT 的 CMOS 反相器的输出功率消耗(Pout)。

DOI:

doi.org/10.1038/s41467-025-57200-2