【知识探索】鳍式场效应晶体管(FinFET)技术解读

日期:2025-06-10阅读:2037

半导体晶体管问世以来,集成电路技术便在摩尔定律的指引下迅猛发展。摩尔定律预言,单位面积上的晶体管数量每两年翻一番,而这一进步在过去几十年里得到了充分验证。

然而,随着技术节点进入纳米级尺度,传统的平面金属氧化物半导体场效应晶体管(MOSFET)面临着严峻的技术挑战。短沟道效应和漏电流问题使得平面MOSFET难以满足深亚微米技术节点的需求。在此背景下,鳍式场效应晶体管(FinFET)应运而生,成为平面MOSFET的继任者,为摩尔定律的持续推进提供了新的可能性。

本文将回顾从平面MOSFET到FinFET的技术演进,探讨其核心原理及未来面临的挑战。

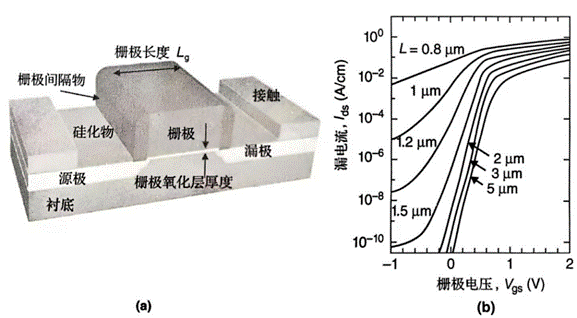

传统的平面MOSFET通过互补金属氧化物半导体(CMOS)技术实现晶体管的缩放,从而提高了集成电路的性能和密度。然而,当技术节点接近亚100纳米级别时,晶体管的几何尺寸的缩小引发了一系列问题。首先,短沟道效应导致栅极对沟道的控制能力下降,使得漏电流显著增加。其次,随着栅长(Lg)的缩短,亚阈值斜率变差,晶体管的开关性能受到影响。

图1展示了传统平面MOSFET在不同栅长下的亚阈值特性模拟结果,表明栅长缩短会导致亚阈值斜率恶化,从而使漏电流(Ioff)显著增加。

图1 (a) 传统平面MOSFET的示意图,(b) 随着栅极长度的缩短,模拟漏电流增加。

漏电流的增加直接导致功耗升高和电路噪声增大,这对移动设备和高性能计算系统的设计提出了严峻挑战。此外,随着晶体管密度的不断提高,掺杂浓度的调整也变得更加复杂,进一步加剧了漏电流问题。尽管通过氧化物层的薄化和高κ介电材料的引入一定程度上缓解了这些问题,但这些改进措施并未从根本上解决短沟道效应和漏电流的挑战。

为了应对平面MOSFET的局限性,半导体领域开始探索新型晶体管结构。

FinFET作为一种三维晶体管结构,通过在硅衬底上形成多个垂直的鳍状结构(fin),实现了对沟道的三维控制。这种结构使得栅极能够更有效地包围沟道,从而增强了栅极的控制能力,减少了漏电流。

FinFET的概念最初由加州大学伯克利分校的研究团队(包括Chenming Hu、Tsu-Jae King-Liu和Jeffrey Bokor等)在SOI(绝缘体硅)衬底上提出。SOI衬底通过减少寄生电容和漏电流,为FinFET的性能优化提供了良好的基础。

随后,三星等公司进一步将FinFET技术扩展到体硅衬底上,通过在鳍下方进行重掺杂来抑制漏电流。尽管这一方法在一定程度上影响了FinFET的性能,但它为大规模制造奠定了基础。

FinFET的核心优势在于其三维结构。与传统平面MOSFET相比,FinFET在相同的技术节点下表现出更低的漏电流和更高的开关比。这使得FinFET能够在深纳米技术节点(如5纳米、3纳米甚至更小)下保持优异的电特性,从而延续了摩尔定律的生命力。

尽管FinFET在技术上取得了显著进步,但其大规模制造和性能优化仍面临诸多挑战。首先,FinFET的三维结构要求制造工艺具有更高的精度,这增加了制造成本和技术难度。其次,随着技术节点的进一步缩小,FinFET的鳍宽和高度需要更加精细化,这对设备的制程能力提出了更高要求。

此外,FinFET的电性能仍需进一步优化。尽管FinFET在抑制漏电流方面表现出色,但其载流能力(如载流子迁移率)可能受到鳍结构和接触电阻的影响。因此,如何在FinFET的结构设计和材料选择中找到平衡点,是未来的关键问题。

FinFET结构及其在微电子器件中的优势

FinFET以其独特的三维结构和显著的性能优势,在微电子器件的设计和制造中发挥了重要作用。

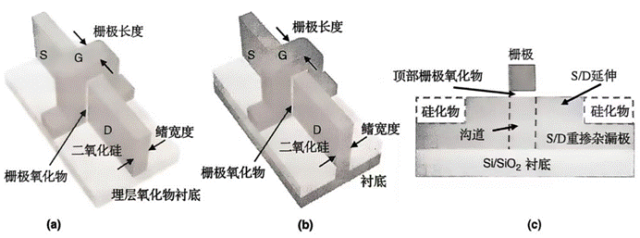

FinFET的基本结构如图2所示,包括在SOI(硅绝缘衬底)或体硅衬底上构建的鳍状晶体管及其纵向剖面图。FinFET的核心特征在于其导电沟道被薄硅鳍包裹,硅鳍构成了器件的主体。从源极到漏极方向测量的鳍厚度直接决定了器件的有效沟道长度。与传统平面MOSFET相比,FinFET的体区设计为超薄,且通过三面控制电场(而非传统的单面顶部控制),大幅提升了对沟道的电气控制能力。

图2 FinFET结构:(a)SOI衬底;(b)体衬底;(c)纵向截面图

这种结构的优化使得FinFET在尺寸缩放方面表现出色。当鳍厚度等于或小于门级长度(Lg)时,FinFET能够有效抑制漏极电流(Off-state leakage current),从而实现更好的性能。此外,由于薄鳍的形成可以采用与栅极图案和刻蚀工具相同的工艺,FinFET的制造工艺相对简单。更重要的是,超薄的体区设计使得体掺杂成为可选项,因为距离栅极几纳米以外的硅区域不再存在,这进一步降低了器件的复杂性。

FinFET的性能与设计

FinFET的多栅配置是其另一个显著特征。在这种配置下,沟道被多个表面的栅极包围,从而实现了对沟道的更好的电气控制。这种设计不仅能够更有效地抑制“关态”漏电流,还能显著提升“开态”驱动电流,增强器件的切换性能。此外,多栅FinFET在模拟电路中表现出更好的本征增益和更低的沟道长度调制能力,这使其在高性能模拟应用中具有独特优势。

FinFET的优势还体现在以下几个方面:更高的速度、更低的漏电、更低的供电电压(Vdd)、更低的功耗、更好的亚阈值摆幅、无随机掺杂波动、更小的变异性、更好的迁移率以及未来的亚阈值设计能力。这些特性使FinFET在高性能计算、低功耗设备和先进的微电子器件中具有广阔的应用前景。

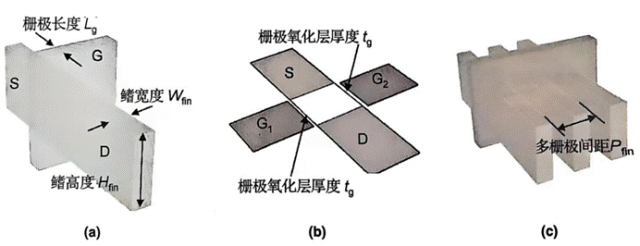

图3展示了FinFET薄体鳍的设计参数及其多栅配置。在设计FinFET时,需要综合考虑多个关键参数:鳍宽、鳍高和鳍间距。

鳍宽:鳍宽的大小直接影响漏极诱导势垒降低(DIBL)效应。较小的鳍宽可以有效降低DIBL,从而提高器件的开关性能。

鳍高:鳍高的选择受到刻蚀技术的限制,需要在布局效率和设计灵活性之间进行权衡。较高的鳍可能会影响器件的缩放能力,而较低的鳍则可能限制电气性能。

鳍间距:鳍间距决定了布局面积,同时影响源/漏(S/D)注入倾角。较小的鳍间距可以提高布局效率,但可能会牺牲器件性能。

图3 (a)双栅-FinFET的鳍参数:(a)示意图;(b)平面图;(c)多栅配置

在FinFET的制造工艺中,栅极优先工艺和源/漏极(S/D)优先工艺是两种主要的技术路线。栅极优先工艺通过先形成栅极并将其作为掩模来注入源极和漏极,这种方法的优点在于源极和漏极与栅极的自对准性较好。然而,在亚100纳米节点及更小尺寸的MOSFET中,由于氧化物的物理缩放极限,必须采用高κ介电质和金属栅极堆栈。这种情况下,栅极优先工艺在后续的注入退火步骤中面临挑战,因为需要在保持堆栈完整性的同时消除注入损伤并获得所需的掺杂分布。为了解决这一问题,S/D优先工艺应运而生。

S/D优先工艺的核心是使用牺牲假栅作为注入掩模,随后在退火步骤后将其移除并构建新的栅极堆栈。这种工艺能够有效解决高κ介电质和金属栅极堆栈的制程难题。

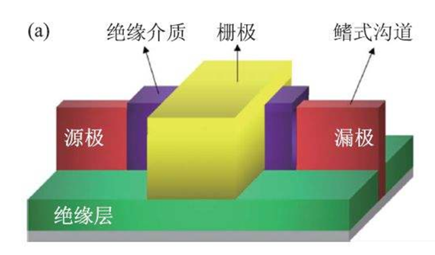

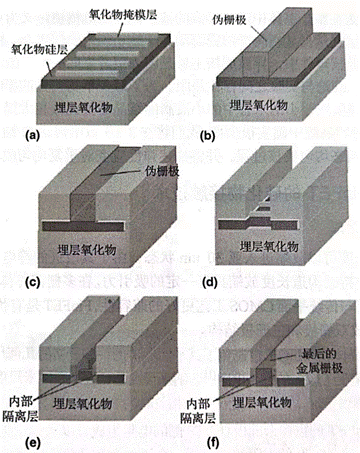

如图4所示,S/D优先工艺在SOI(硅壳体)衬底上形成FinFET的过程主要包括以下步骤:

首先,通过氧化物掩模层进行图形化并刻蚀至SOI;然后,在图形化氧化物层上沉积、图形化和刻蚀形成假栅,并去除暴露的硬掩模氧化物,随后进行S/D形成和硅化;接着,沉积绝缘体填充接触沟槽,并进行平坦化;随后,去除假栅,露出图形化的硬掩模,通过该掩模将鳍图形通过各向异性刻蚀转移到下面的硅层;之后,在S/D侧壁形成内隔离层,以确保栅极与扩展的源极和漏极之间有足够的分离;最后,在栅极沟槽中沉积形成栅极堆栈。

图4 SOI衬底FinFET的形成原理图:先源极和漏极、后主体鳍的制作方法

半导体行业在FinFET的研发和量产方面取得了显著成就。晶圆代工厂已经实现了16纳米/14纳米FinFET的量产,10纳米FinFET的开发也在进行中。然而,随着技术节点的不断缩小,传统FinFET的扩展性逐渐受到限制。

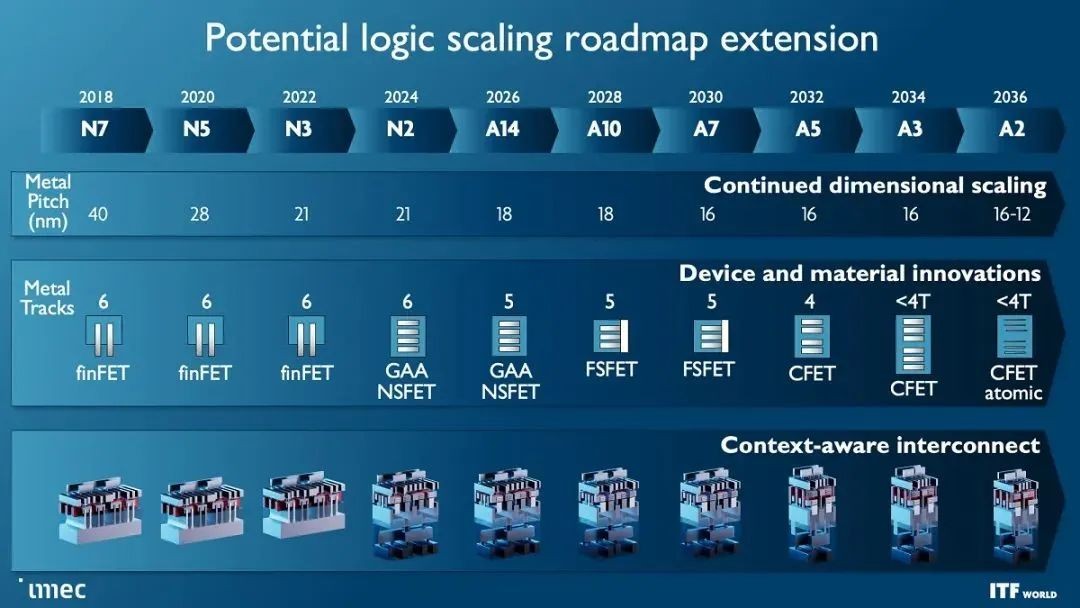

根据IMEC的技术路线图,7纳米节点提供了两种晶体管选择:FinFET和横向环栅纳米线FET(横向纳米线FET)。对于5纳米节点,更倾向于采用横向纳米线FET。横向纳米线FET本质上是FinFET从双栅和三栅到全环栅结构的演进,这种结构通过增加栅极面积,进一步提升了栅极对载流子的控制能力,从而更有效地关断器件。

比利时微电子研究中心(IMEC)发表1纳米以下制程蓝图,分享对应晶体管架构研究和开发计划

比利时微电子研究中心(IMEC)发表1纳米以下制程蓝图,分享对应晶体管架构研究和开发计划

尽管横向纳米线FET在静电特性上可能优于FinFET,但其制造工艺更加复杂,尤其是在器件底部的工艺处理上面临更大的挑战。FinFET在实际应用中仍然面临一些关键挑战,包括阈值电压的调节、栅极与源极和漏极顶部/底部之间的边缘电容、寄生电阻以及器件的可变性。这些问题在一定程度上限制了FinFET在更小技术节点中的性能优化。

综上所述,FinFET凭借其独特的三维结构和优异的性能,成为亚100纳米半导体器件的核心技术。尽管其制造工艺复杂且面临一些技术挑战,但随着S/D优先工艺的不断优化和高κ介电质与金属栅极堆栈的应用,FinFET在16纳米/14纳米节点上的成功量产已经证明了其技术的成熟度。然而,随着技术节点的进一步缩小,可能需要转向更具前瞻性的结构,如横向纳米线FET,以满足未来的性能需求。

参考资料:

半导体集成电路制造手册Semiconductor Manufacturing Handbook