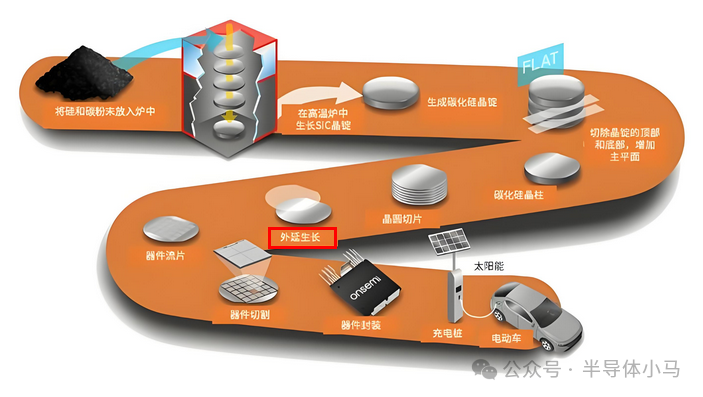

【知识探索】半导体外延生长核心技术:生长机制与设备原理

日期:2025-09-19阅读:1730

外延(Epitaxy)源自希腊语“Epi”(在上)与“taxis”(排列)的组合,特指在单晶衬底上沿其晶向生长单晶薄膜的精密工艺。生长的外延层与衬底保持一致的晶体取向和晶格结构,可通过原子级控制实现厚度(微米级)、掺杂浓度及晶体质量的精准调控,形成“外延片=衬底+外延层”的核心结构。

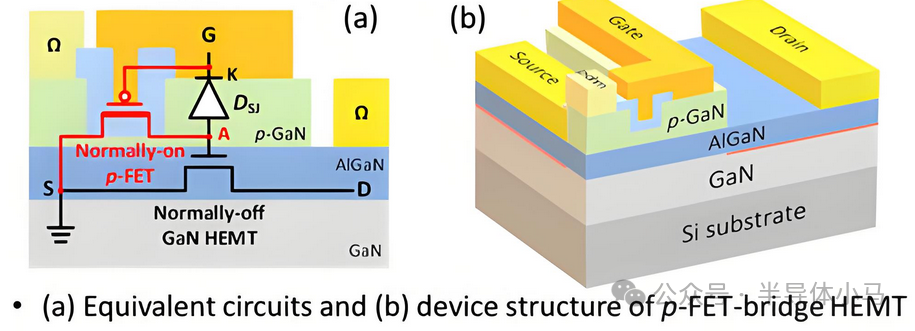

根据材料异同,外延可分为同质外延(如Si on Si)与异质外延(如GaAs on Si),前者保障晶格匹配性,后者拓展材料组合可能性,为多功能器件制备奠定基础。

1)体单晶材料的局限性与外延技术的突破

传统体单晶材料存在两大核心瓶颈:

一是缺陷密度高,自然生长过程中易形成位错、空位等晶格缺陷,影响载流子迁移率;

二是电阻率不均,难以同时满足器件对高击穿电压(需高电阻率)与低串联电阻(需低电阻率)的矛盾需求。

外延技术通过以下机制实现突破:

原子级生长控制:采用气相外延(如HVPE)等方法,使原子沿衬底晶格有序排列,显著降低缺陷密度。例如,硅外延层的晶体完整性远高于体硅,可实现±2%以内的厚度误差控制;

核心价值:从材料优化到器件性能跃升

外延技术的核心价值体现在对半导体器件性能的全方位重塑,具体包括三大维度:

第三代半导体外延的不可替代性:在新能源车逆变器(SiC外延层成本占芯片总成本20%)、高铁电源(GaN高频特性降低能耗30%)等场景中,外延层的晶体质量直接决定器件良率与长期稳定性,成为高温(>300℃)、高频(>10 GHz)、高功率(>1000 V)应用的“刚需工艺”。

外延技术通过将材料制备与器件制造工艺深度融合,不仅解决了体单晶材料的固有缺陷,更成为突破半导体性能极限的核心引擎。从传统硅基芯片到第三代宽禁带器件,外延层的“性能Buff”效应贯穿半导体产业升级全过程,支撑着新能源车、量子计算等前沿领域的技术突破。

外延生长根据材料组合、晶格匹配度及应力状态的差异,可分为同质外延、异质外延、应变外延和非应变外延四类,其技术特性与应用场景各具显著差异。以下从材料组合、晶格匹配、应力状态及器件应用四个维度进行对比分析:

1)晶格失配与应力产生原理

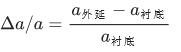

异质外延中,衬底与外延层的晶格常数差异是应力产生的核心原因。当外延层材料晶格常数大于衬底时(如SiGe/Si系统),外延层会受到压应力;反之则产生拉应力。晶格失配率(Δa/a)可通过公式计算:

例如,GaN与蓝宝石衬底的晶格失配率高达16%,导致原子排列错配概率显著增加,需通过“纳米图形化AlN模板”等技术抑制位错15。而同质外延因材料相同,晶格常数完全匹配,可实现无应力的二维层状生长(Frank-Van-Der-Merwe模式)16。

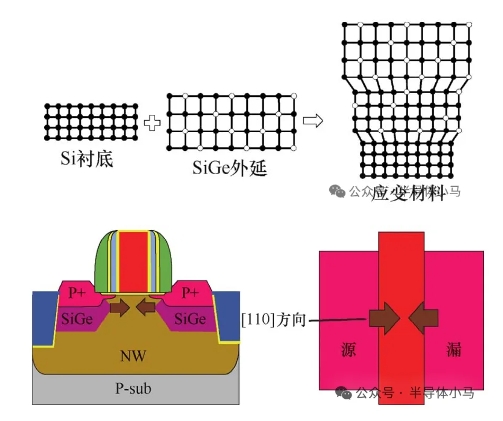

2)应变外延的典型案例:SiGe/Si系统的性能增强机制

在65/45nm CMOS工艺中,PMOS源漏区采用SiGe应变外延技术,利用SiGe与Si的晶格常数差异(Ge原子半径大于Si),在Si衬底上形成压应力外延层。这种压应力会改变Si的价带结构,降低空穴有效质量,使空穴迁移率提升30%-50%,最终导致饱和电流(Idsat)增加35%。类似地,在松弛的SiGe层上外延Si可引入拉应力,提升电子迁移率,进一步优化器件响应速度。

详情可参考:先进工艺技术--应变硅技术

技术关键点:外延生长模式直接影响薄膜质量——层状生长(2D)适用于晶格匹配系统(如Si/Si),岛状生长(3D)适用于高失配系统(如GaN/蓝宝石),而Stranski-Krastanov模式(先2D后3D)则是应变外延的典型生长方式(如SiGe/Si)。

四类外延技术中,同质外延以高晶体质量为核心优势,异质外延通过材料组合实现功能扩展,应变外延则通过应力调控突破载流子迁移率极限,共同支撑了半导体器件向高功率、高频、高集成度方向的发展。

半导体外延生长的核心在于原子尺度的动态调控,其过程可通过“原子迁移-成核-生长”三阶段模型进行系统描述。该模型结合分子动力学模拟,揭示了温度、表面能等关键参数对薄膜质量的决定性影响,并通过层状、岛状及Stranski-Krastanov(S-K)模式的演变规律,解释了外延层表面形貌的形成机制。

1)三阶段生长动力学模型

外延生长的原子级过程遵循严格的时序逻辑,具体可分为以下三个阶段:

原子迁移阶段:源原子(如Ga、N原子)在衬底表面发生吸附、扩散与脱附行为,其迁移长度直接受温度影响。分子动力学模拟显示,温度通过改变原子热运动能量调控扩散能力——当温度过低(如GaN生长低于980℃),原子迁移能不足导致扩散长度缩短,未充分迁移的原子易形成点缺陷聚集,使X射线衍射(XRD)半高宽(FWHM)恶化至800 arcsec以上;而温度过高(如GaN生长高于1120℃)则会因原子迁移率过高引发三维岛状生长,表面粗糙度(RMS)从0.2 nm陡增至1.5 nm以上。

三阶段模型核心特征

2)生长模式与表面形貌演变

外延层的宏观形貌由生长模式决定,主要包括以下三种典型机制,其转变受晶格匹配度、应变状态及工艺参数共同调控:

1. 层状生长(Frank-van der Merwe模式)

当外延层与衬底晶格匹配度高且表面能较低时,原子优先以二维层状方式生长。例如,硅气相外延中,Si原子通过“传输-吸附-反应-脱附-逸出-加接”六步过程,在衬底表面实现横向二维逐层生长,其形貌与晶面“平台-台阶-扭转位置”结构紧密相关。该模式下,外延层表面平整度高,RMS可控制在0.5 nm以下,适用于高频器件等对界面质量要求严苛的场景。

2. 岛状生长(Volmer-Weber模式)

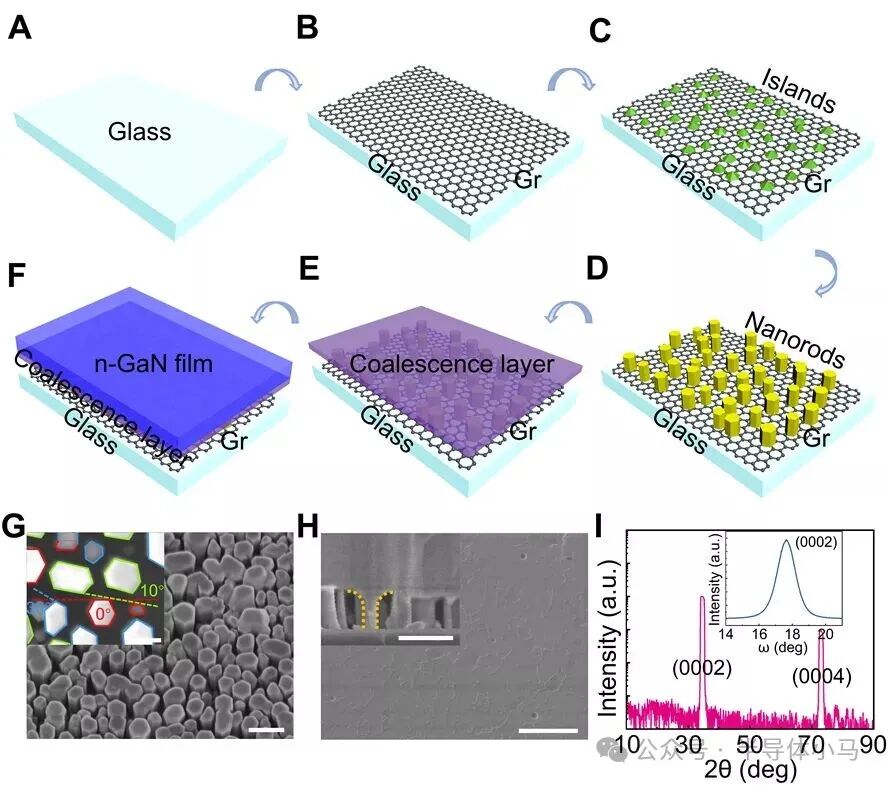

晶格失配度大或表面能较高时,原子更易形成三维岛状结构。以GaN在蓝宝石衬底上的异质外延为例,当温度超过1120℃时,Ga原子表面迁移率过高,突破二维成核能垒,直接形成孤立三维岛,导致表面粗糙度显著增加。此类生长模式易引入晶界和位错,需通过温度场仿真优化(如PID温控技术)抑制三维岛的过度生长。

3. Stranski-Krastanov(S-K)模式

该模式为层状向岛状的过渡形态,常见于应变外延系统。初始阶段,外延层以二维层状生长(通常1-3个原子层),当应变积累超过临界值(如AlN在蓝宝石衬底上的应变阈值),体系通过形成三维岛释放应变,完成“层-岛”转变。此过程伴随位错等缺陷生成,可通过“纳米图形化AlN模板”(NPAT)等技术调控侧向外延方向,将位错密度抑制至~10⁴ cm⁻²量级。

上述生长模式的动态调控是外延工艺的核心挑战。通过优化温度梯度(如GaN MOCVD中温度梯度每增加1℃/mm,位错密度上升50%)、气流场分布(区域划分进气调节实现均匀输运)及衬底表面预处理(如4H-SiC原位刻蚀形成原子台阶),可实现对“原子迁移-成核-生长”全流程的精准控制,为高性能半导体器件奠定材料基础。