【国际论文】英国布里斯托大学:4 kV β-Ga₂O₃ 沟槽肖特基势垒二极管在高压阶跃应力作用下的导通电流衰减

日期:2025-10-21阅读:410

由英国布里斯托大学的研究团队在学术期刊 Applied Physics Letters 发布了一篇名为 Degradation of on-current in 4 kV β-Ga2O3 trench Schottky barrier diodes under high voltage step stressing(4 kV β-Ga2O3 沟槽肖特基势垒二极管在高压阶跃应力作用下的导通电流衰减)的文章。

背 景

β-Ga2O3 为电动交通、电力转换、电网等领域开辟了广阔前景。研究预测 Ga2O3 有望在中高压直流电力转换器中替代碳化硅(SiC)。然而,Ga2O3 缺乏 p 型掺杂与导电性,导致器件结构仅限于单极性肖特基二极管,而双极性结构需与 p 型 NiOx 异质集成。肖特基界面处的峰值电场导致高漏电流,阻碍了肖特基二极管在安培级 kV 器件中的实际应用。沟槽肖特基势垒二极管(TSBD)是一种先进结构,通过侧壁 MOS 电容 fin 将峰值电场转移至 fin 内部远离器件表面,从而实现表面电场抑制(RESURF)。RESURF 效应显著抑制反向漏电流,同时实现优异击穿电压;目前采用场板边缘封装结构时已报道高达 2.9kV 的击穿电压,失效主要发生在 fin 角部的介质层。侧壁与 Ga2O3 介质界面及 fin 取向会影响电流传导能力——正向应力测试条件下可观察到界面处电荷捕获现象。目前针对该器件系统在高反向应力条件下的可靠性研究极为有限,这对未来产业化至关重要。

主要内容

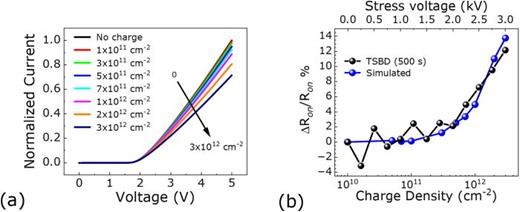

本文报道了基于 β-Ga2O3 的沟槽肖特基势垒二极管的可靠性,其击穿电压达 4kV,巴利加优值约为 1GW/cm2。器件在 250V 递增下承受高达 3kV 的反向电压应力,并在每次步进应力后评估导通状态特性。阶跃应力测试表明:当应力施加至 2.25kV 时导通电阻增量 <3%,但 3kV 应力下增量达 13%,经 3 小时休整后可完全恢复。高反向偏压应力下导通特性退化(电流崩溃)归因于 fin角部附近负电荷捕获效应,该效应导致 fin 净导电面积缩减。通过漂移扩散模拟可复现该电流退化现象,实验观测的 13% 退化需对应约 3×1012 cm-2 的困陷电荷密度。本研究揭示了介电特性与电荷困陷对 Ga2O3 等超宽带隙材料可靠性与性能的关键影响。

结 论

本研究成功制备了击穿电压达 4kV、功率 FOM 值约 1GW/cm2 的沟槽肖特基势垒二极管,并对其短期应力下的行为进行了研究。在反向偏压条件下,对二极管施加阶梯式应力(最高达 3kV),并在每个应力阶梯后测量导通特性,结果显示导通电流随应力电压增加而略有下降。在 2.25kV 应力下导通电阻劣化率低于 3%,3kV 应力下为 13%——这凸显了 Ga2O3 器件在可靠高压应用中的潜力。劣化根源被精确定位为高电场下沟槽拐角处的电荷注入,而非 Ga2O3 材料本身的限制。存储电荷在导通状态测量期间调制耗尽区,缩小净导电面积导致导通电阻增大。本研究揭示了高压应力对 β-Ga2O3 沟槽肖特基势垒二极管性能的影响,深入阐释了器件退化的驱动机制。

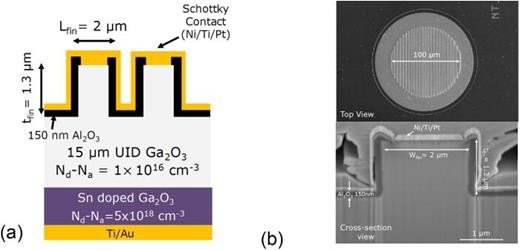

图1. (a) Ga2O3 TSBD的横截面示意图。(b) TSBD的顶视图及横截面SEM图像。

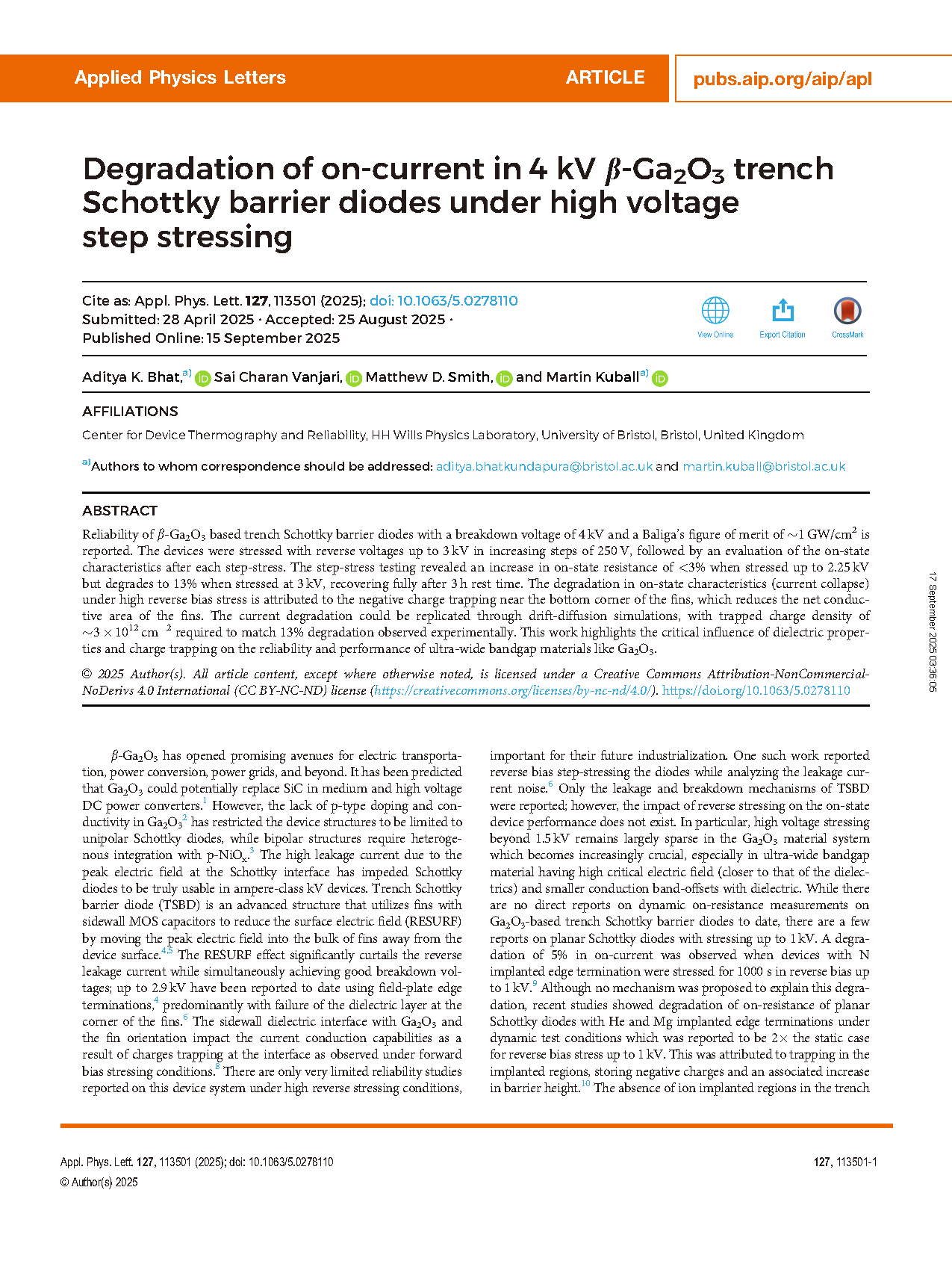

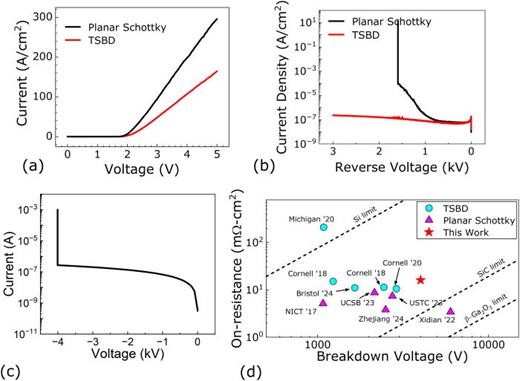

图2. (a) 二极管正向特性曲线;(b) 反向特性曲线(最高至 3kV)。TSBD 的击穿电压高于 3kV;(c) 采用 10kV 测试装置测得的击穿特性曲线,通过注入电流并测量电压显示 TSBD 在 4kV 时发生击穿;(d) 本研究制备的 TSBD 性能指标图,与文献报道数据进行对比。

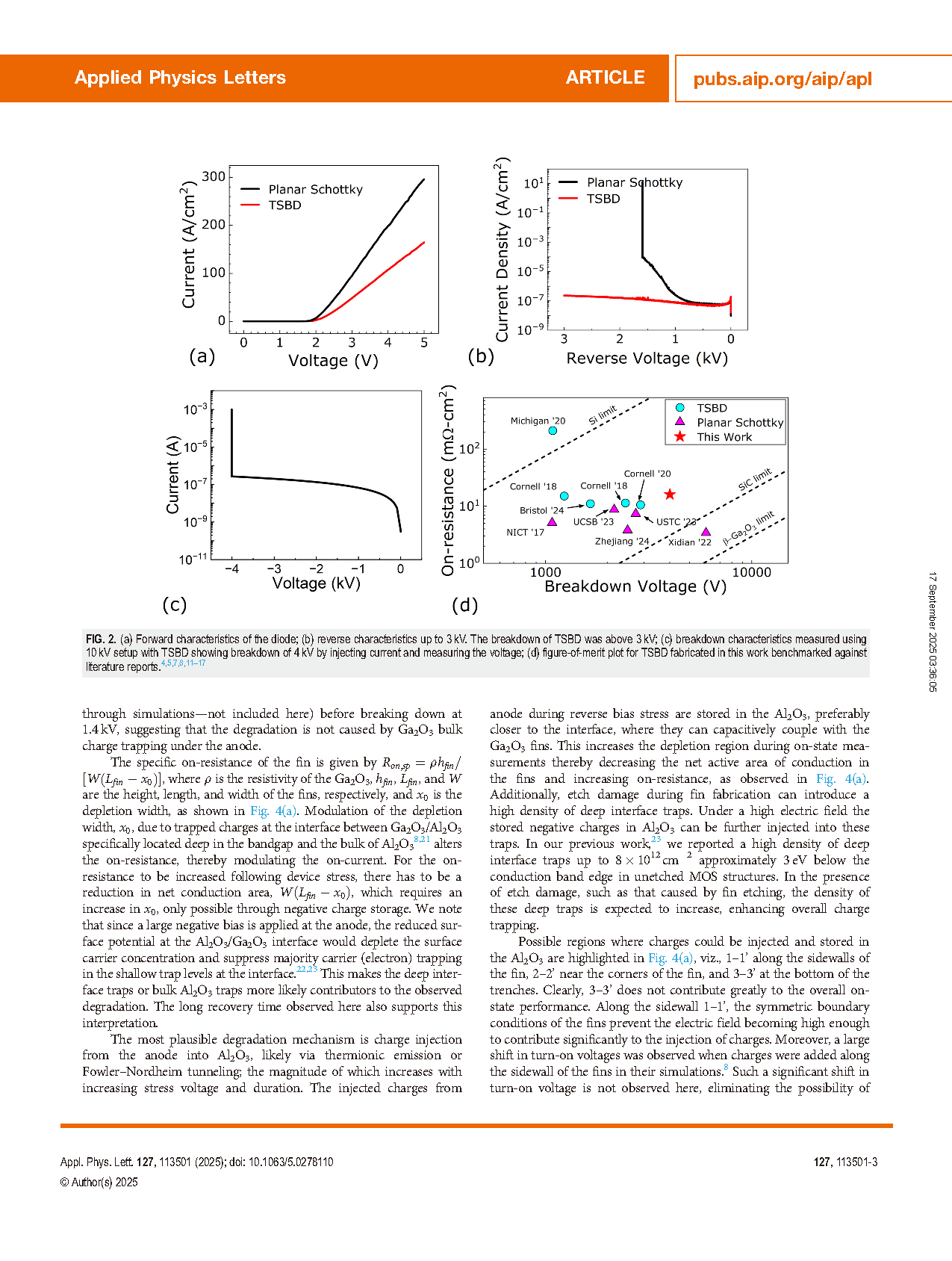

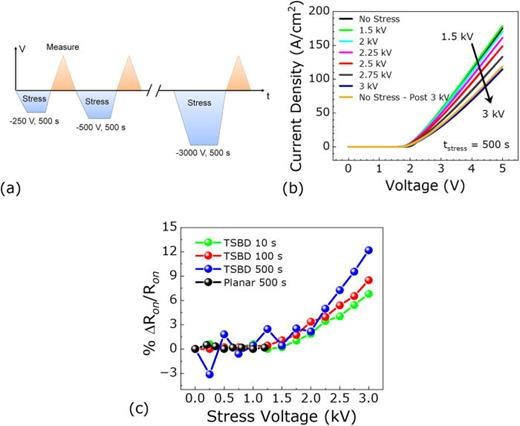

图3. (a) 可靠性测量的时间尺度表示;(b) 不同应力电压下经过 500 s 应力处理后的二极管导通特性;(c) 每次应力电压处理后导通电阻(Ron)的百分比增长量(相对于平面二极管)。

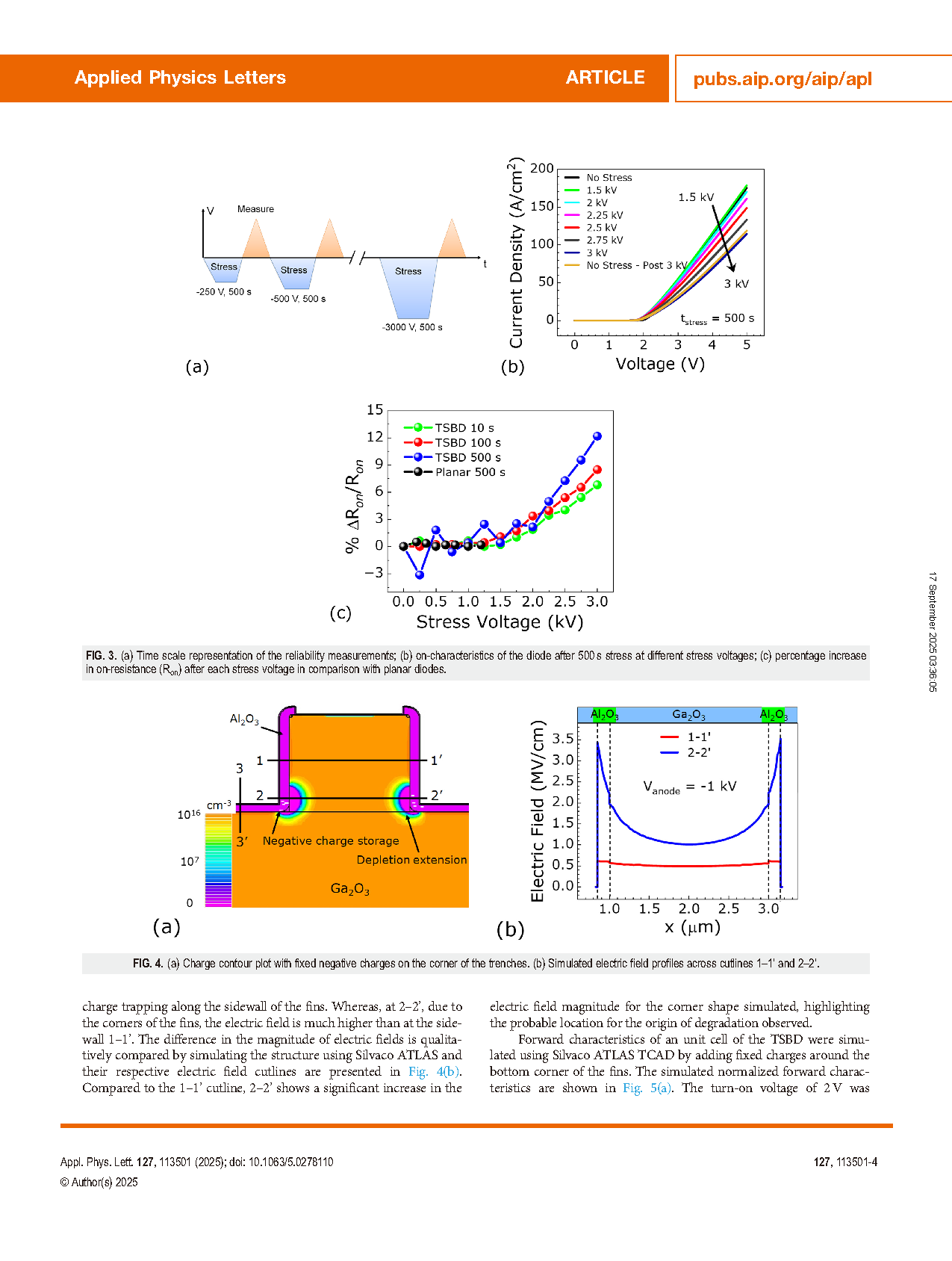

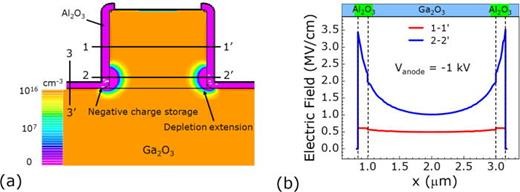

图4. (a) 沟槽拐角处固定负电荷的电荷分布图。(b) 截面1–1'和2–2'处的模拟电场分布曲线。

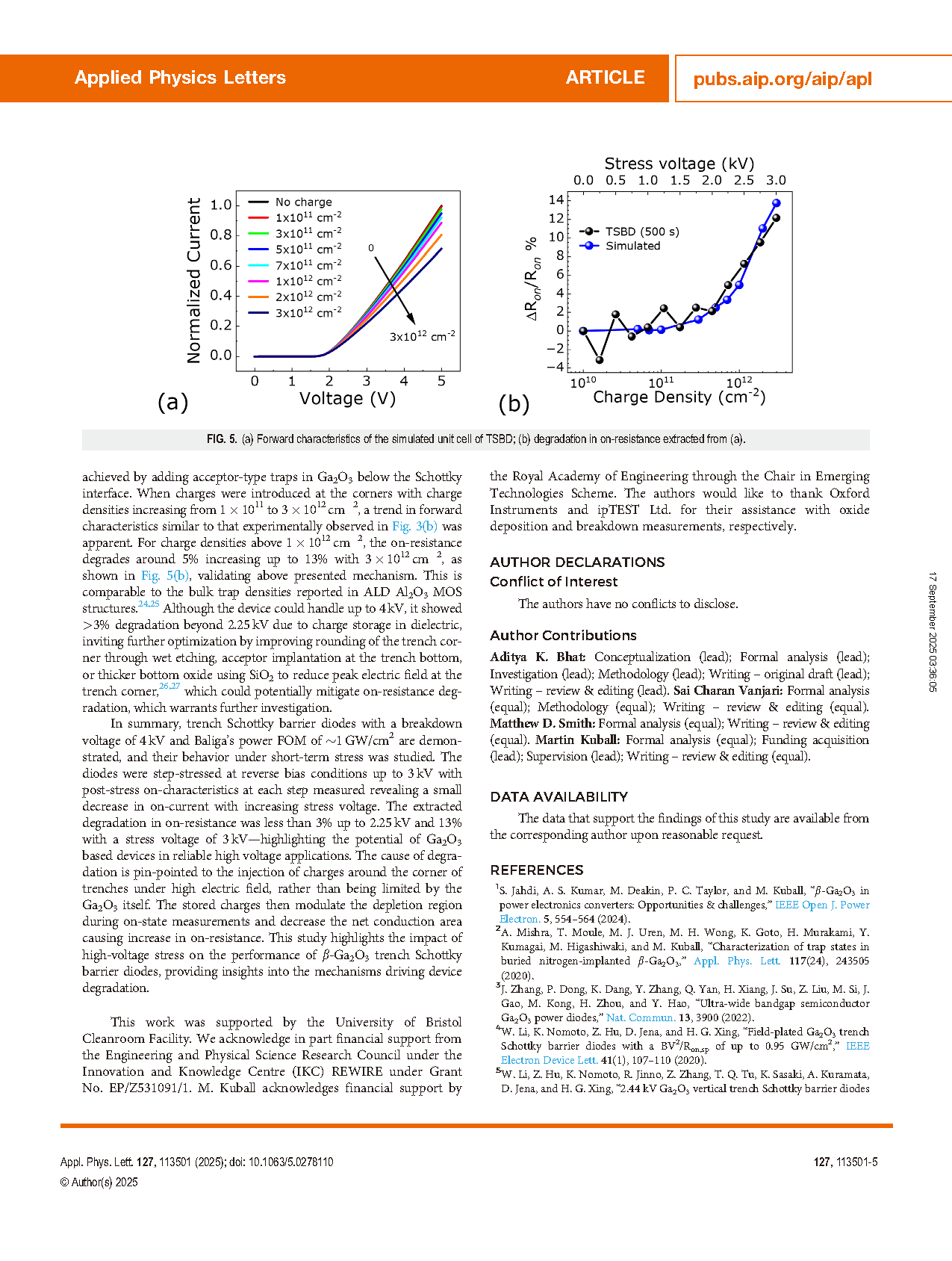

图5. (a) TSBD 模拟单元格的正向特性曲线;(b) 从 (a) 中提取的导通电阻衰减曲线。

DOI:

doi.org/10.1063/5.0278110