【国际论文】APL丨英国布里斯托大学:双漂移层结构用于最小化2.7kV β-Ga₂O₃ (001)垂直沟槽肖特基势垒二极管的导通电阻

日期:2026-03-20阅读:17

由英国布里斯托大学的研究团队在学术期刊 Applied Physics Letters 发布了一篇名为 Double drift layers to minimize on-resistance in 2.7-kV β-Ga2O3 (001) vertical trench Schottky barrier diodes(双漂移层结构用于最小化 2.7kV β-Ga2O3 (001)垂直沟槽肖特基势垒二极管的导通电阻)的文章。

背 景

超宽带隙(UWBG)氧化镓(β-Ga2O3)具有极高的临界电场,使其在千伏级高压功率电子器件中具有巨大的应用前景。垂直 β-Ga2O3 功率器件通常在导电衬底上生长数微米厚的轻掺杂或非故意掺杂(UID)外延漂移层,以在外延层内承担关断状态下的高压。在平面肖特基势垒二极管(SBD)中,电场峰值集中在金属与半导体的接触界面,容易引发热发射驱动的反向漏电流,严重限制了器件的击穿电压。为了解决漏电问题,引入了沟槽式结构(TSBD),利用降低表面电场(RESURF)效应来提升耐压性能。然而,这种改进通常以牺牲特定导通电阻(Ron,sp)为代价,因为沟槽的刻蚀和介电层占据了原本属于肖特基接触的空间,减小了电流流通的有效面积。

主要内容

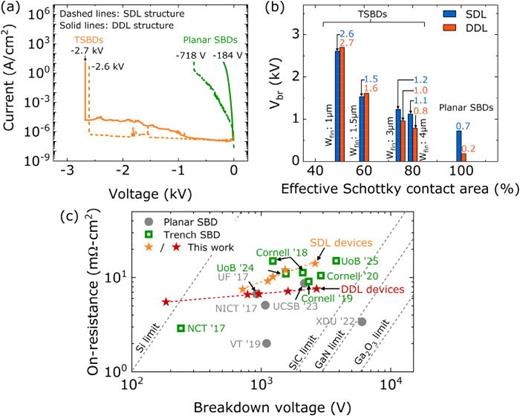

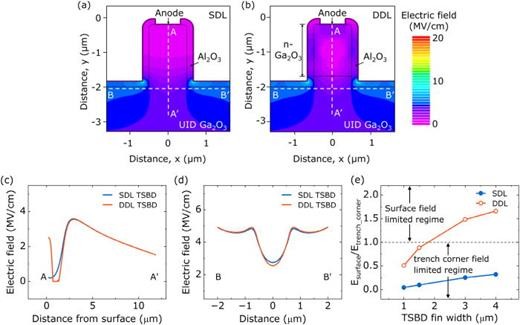

通过采用双漂移层(DDL)肖特基势垒二极管(TSBD)架构,在 β-氧化镓(β-Ga2O3)沟槽肖特基势垒二极管中实现了更优的导通电阻(Ron,sp),且无需牺牲击穿电压——该架构在非掺杂漂移区(UID)上方叠加了硅掺杂漂移层。与单 UID 漂移层 TSBD 相比,DDL TSBD 的 Ron,sp 降低 46 %,同时保持 2.6-2.7 kV 的相似 Vbr 值。由此,DDL TSBD 设计将巴利加优值从传统 TSBD 的 481 MW/cm2 提升至 959 MW/cm2,实现两倍性能提升。Silvaco TCAD 仿真进一步证实,两种结构在沟槽拐角处均呈现相似的峰值主导电场,与其相近的击穿电压相一致。虽然 TSBD 中缩小 fin 宽度能通过改善表面场效应来提升 Vbr,但研究团队证明该效应在 DDL TSBD 中得到显著放大,从而实现了传统 Ron,sp–Vbr 轨迹的重大转变。

创新点

● 该研究首次提出并实现了双漂移层(DDL)TSBD 架构,在原有的 UID 漂移层顶部增加了一层通过 Si 离子注入形成的 Si 掺杂漂移层。

● 通过在 fin 区域选择性地进行 Si 注入,显著提高了 fin 部分的导通能力(降低电阻),同时在漂移区深处保持低掺杂密度以维持高击穿电压。

● 与传统的单一 UID 漂移层 TSBD 相比,该 DDL 设计在保持相似击穿电压(~2.6-2.7 kV)的情况下,将特定导通电阻降低了 46 %。巴利加优值(BFOM)从传统结构的 481 MW/cm2 显著提升至 959 MW/cm2。

●研究表明,DDL 结构能更显著地增强 RESURF 效应,从平面结构到沟槽结构的 BFOM 提升倍数高达约 160 倍,而单一 UID 结构仅提升约 7 倍。

总 结

研究团队提出了一种双漂移层(DDL)架构,重新定义了沟槽肖特基势垒二极管(TSBD)中特定导通电阻(Ron,sp)与击穿电压(Vbr)之间的平衡关系。通过对 fin 区顶部进行选择性掺杂,DDL TSBD 在保持高击穿电压的同时,实现了远低于传统单漂移层 TSBD 的 Ron,sp 值。与单漂移层器件(其击穿电压提升需以 Ron,sp 显著恶化为代价)不同,DDL 设计通过有效调控击穿限制电场,实现了 Ron,sp-Vbr 轨迹的转变,使基本功能指标(BFOM)提升至原来的 2 倍。这证明 fin 掺杂技术(而非仅依赖几何结构)可用于调控垂直 Ga2O3 TSBD 的性能。

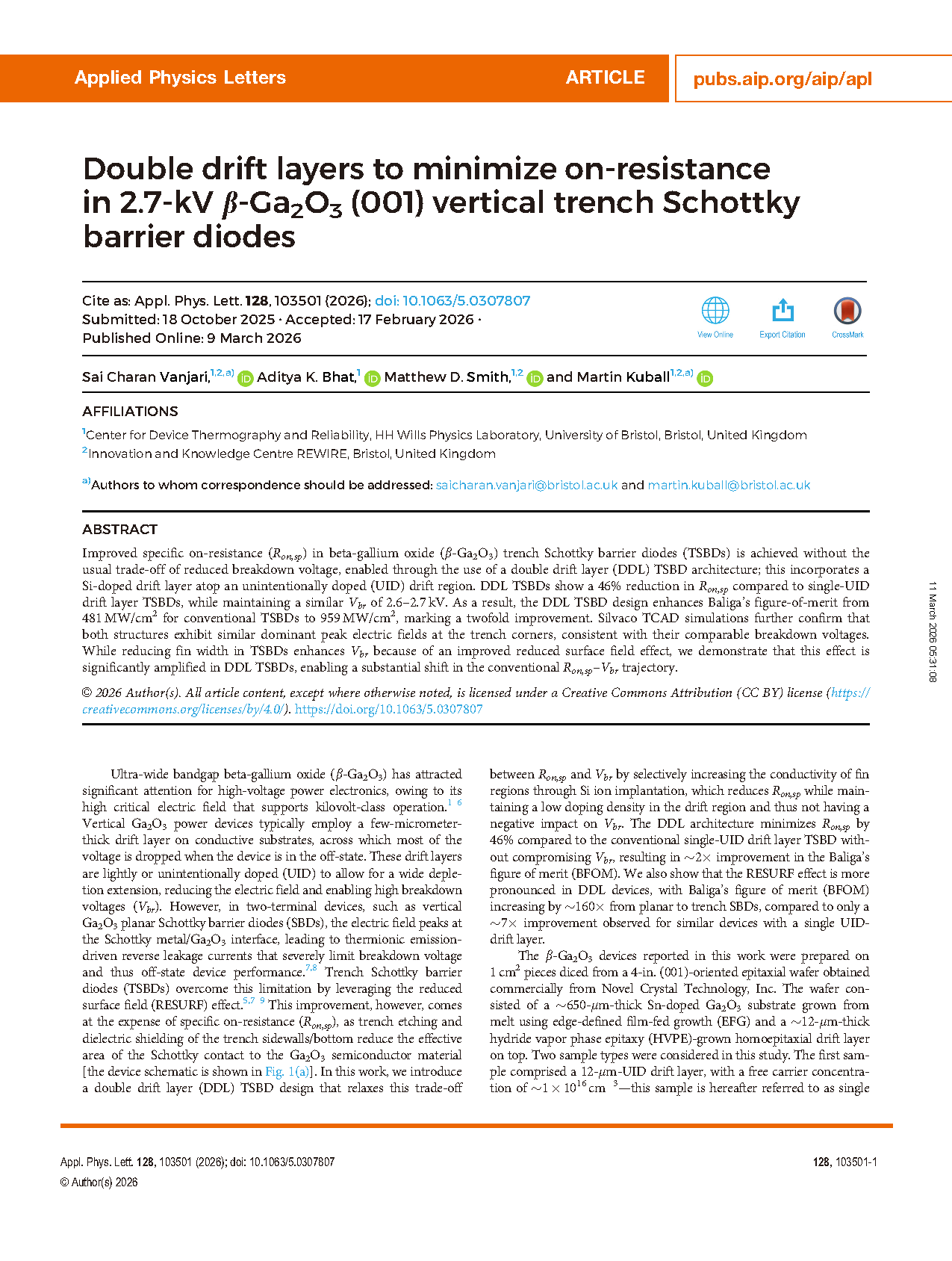

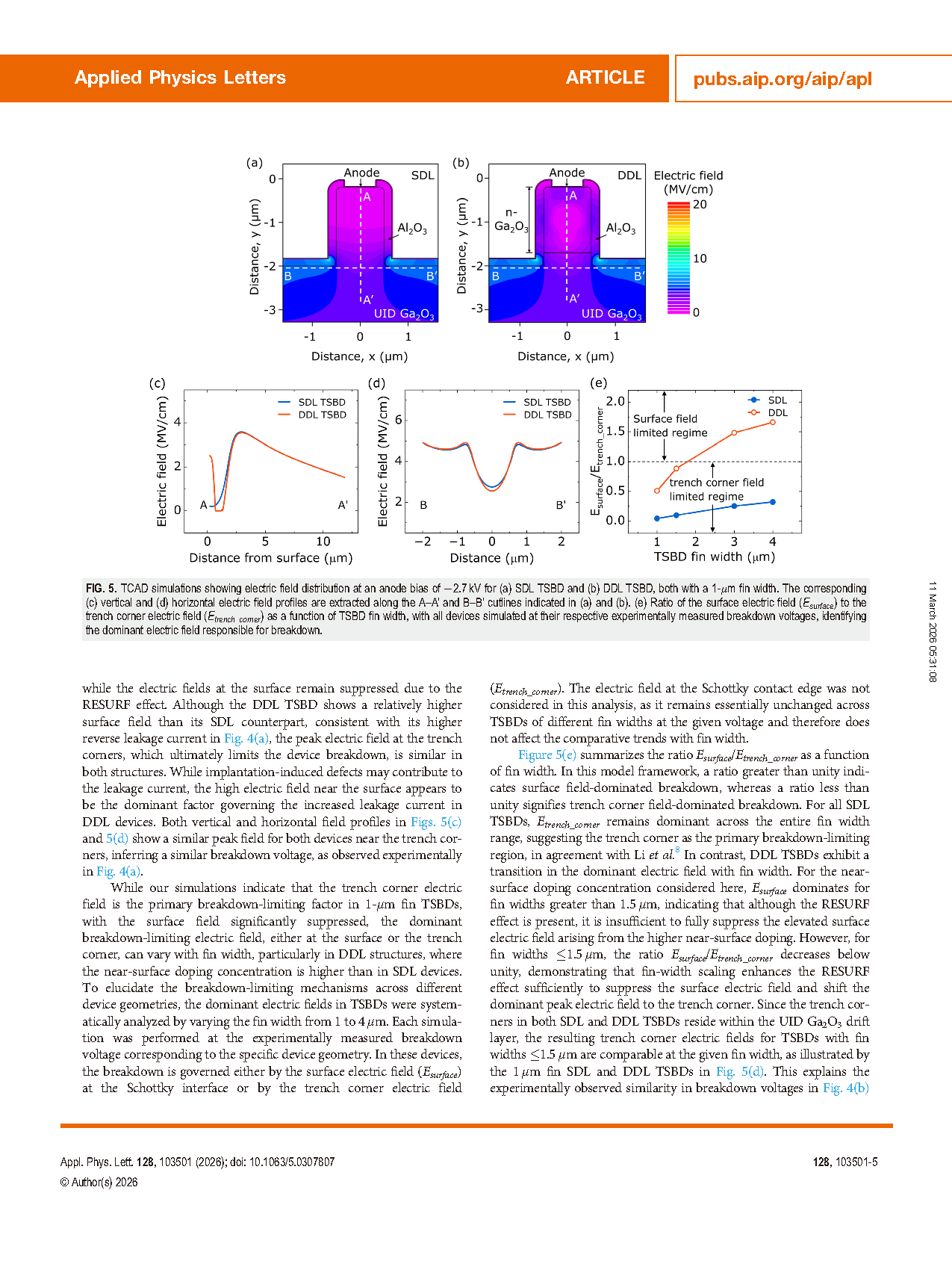

图1. (a) 单漂移层(SDL)结构上的 Ga2O3 沟槽肖特基势垒二极管(TSBD),其具有 12 μm 非故意掺杂 (UID) Ga2O3 漂移层;(b) 双漂移层(DDL) TSBD 结构,其中 12 μm UID 漂移层的上部 1.5 μm 经硅掺杂形成轻掺杂 n 型 Ga2O3 区域;(c) 制备的 DDL TSBD 截面 SEM 图像,其 fin 宽度为 1 μm。

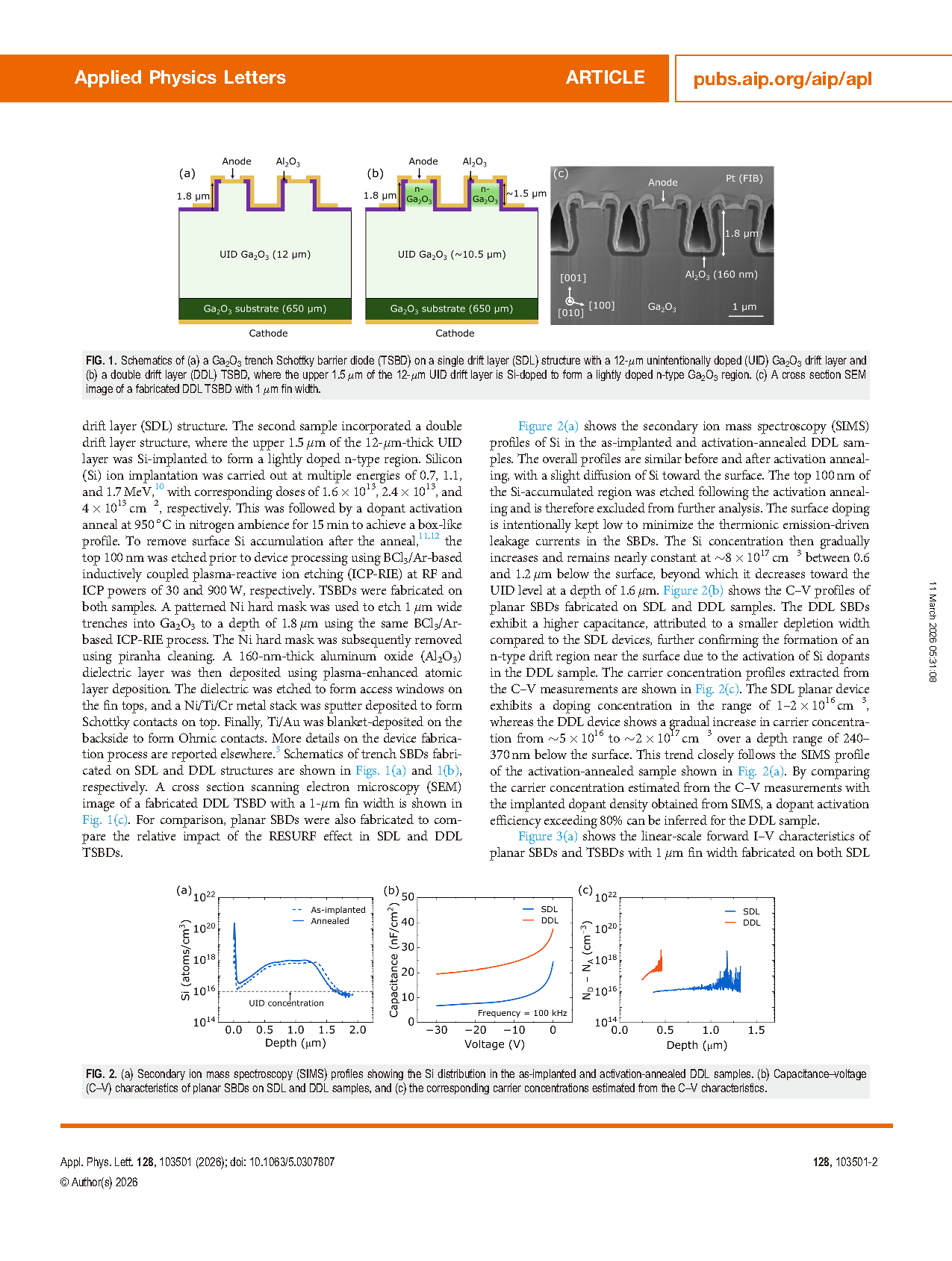

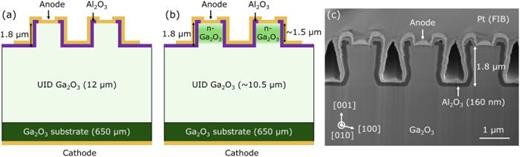

图2. (a) 二次离子质谱(SIMS)剖面图,显示注入后及活化退火处理的DDL样品中硅的分布情况。(b) SDL 和 DDL 样品上平面 SBD 的电容-电压(C-V)特性曲线,以及(c) 根据 C-V 特性估算的对应载流子浓度。

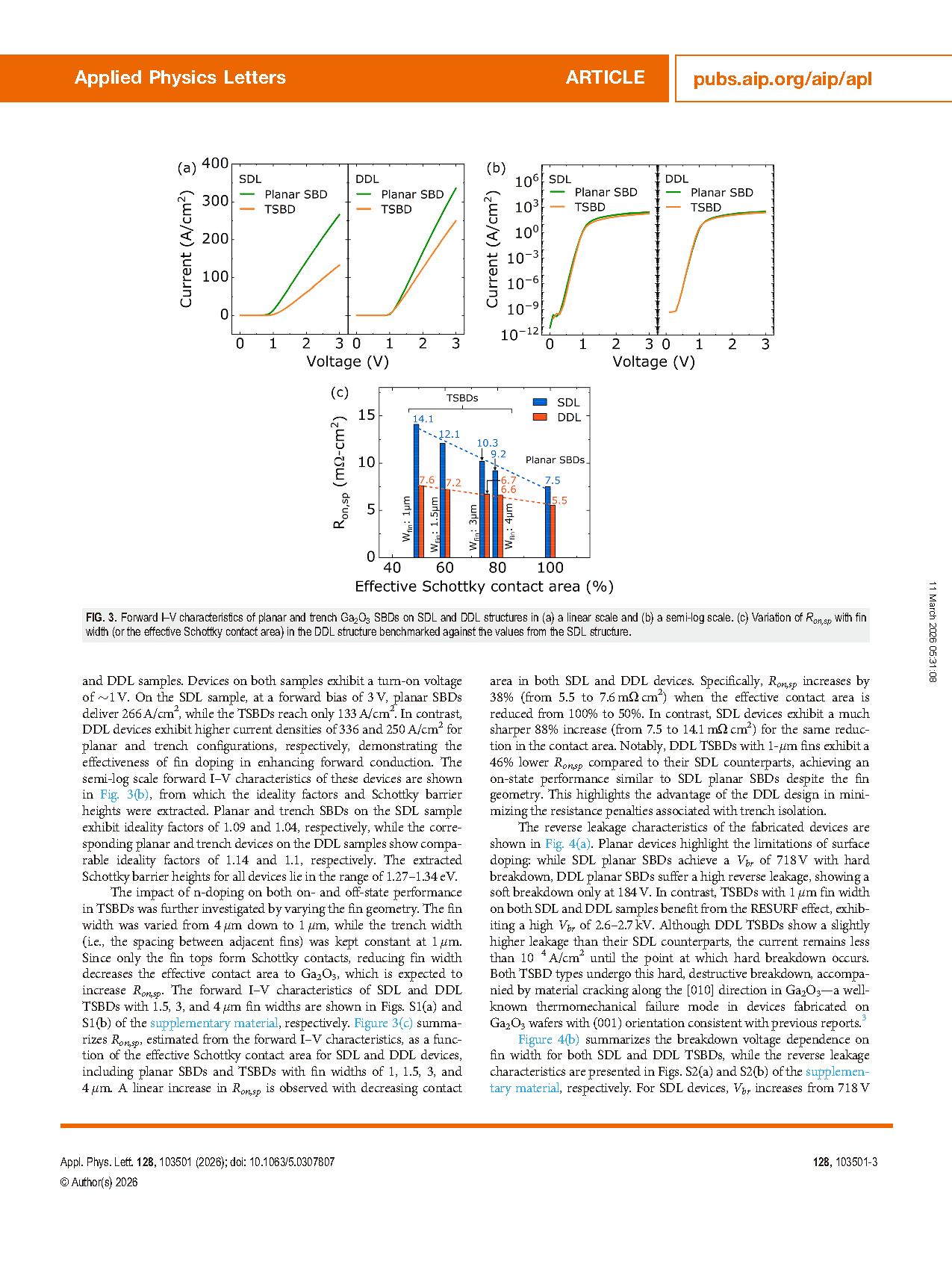

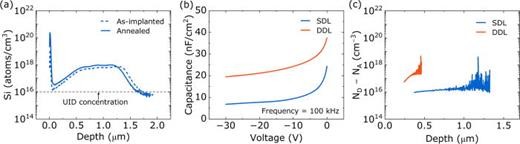

图3. 基于 SDL 和 DDL 结构的平面式与沟槽式 Ga2O3 SBD 正向 I-V 特性曲线:(a)线性坐标系;(b)半对数坐标系。(c)DDL 结构中 Ron,sp 随栅极宽度(或有效肖特基接触面积)的变化趋势,与SDL结构数据进行对比。

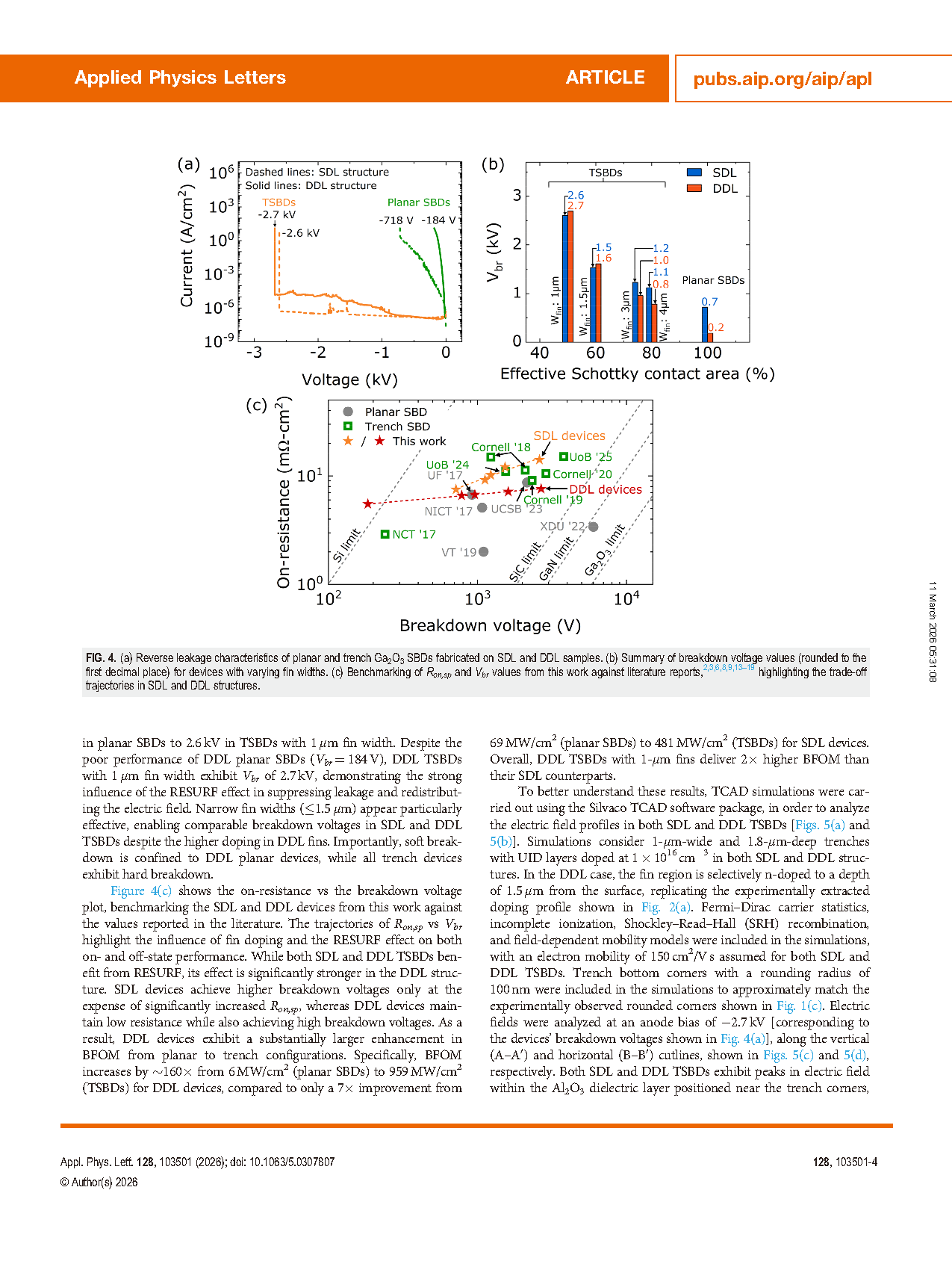

图4. (a) 基于 SDL 和 DDL 样品制备的平面型与沟槽型 Ga2O3 SBD 的反向漏电流特性曲线。(b) 不同 fin 宽度器件的击穿电压值汇总(精确至小数点后一位)。(c) 本研究中 Ron,sp 与 Vbr 值与文献报道的对比分析,重点展示 SDL 与 DDL 结构中的权衡轨迹。

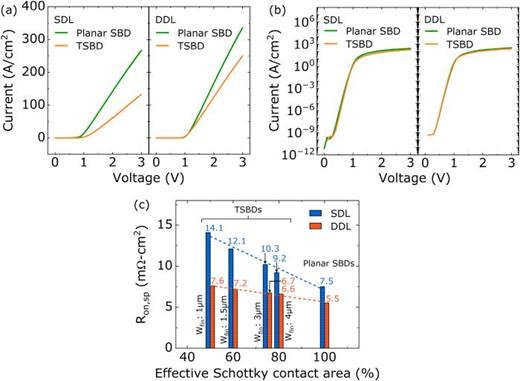

图5. TCAD 模拟显示在阳极偏压为 −2.7 kV 时,(a) SDL TSBD 和 (b) DDL TSBD 的电场分布,两者均采用 1 μm fin 宽度。沿 (a) 和 (b) 中标示的 A–A' 与 B–B' 剖面线提取的对应 (c) 垂直及 (d) 水平电场分布曲线。(e) 随 TSBD fin 宽度变化,表面电场 (Esurface) 与沟槽拐角电场 (Etrench_corner) 之间比值的关系曲线,所有器件均在各自实验测得的击穿电压下进行模拟,从而识别出导致击穿的主导电场。

DOI:

doi.org/10.1063/5.0307807