【会员论文】JAC丨浙江大学杨德仁院士、张辉教授&杭州镓仁半导体研究团队:铸造法制备 6 英寸(100)晶面β‑Ga₂O₃单晶及其性能表征

日期:2026-04-22阅读:125

由浙江大学、杭州镓仁半导体有限公司的研究团队在学术期刊 Journal of Alloys and Compounds 发表了题为 The Growth and Characterization of 6‑inch (100) β‑Ga₂O₃ Single Crystals Grown by a Casting Method (铸造法制备 6 英寸(100)晶面 β‑Ga₂O₃ 单晶及其性能表征)的研究论文。

背 景

β‑Ga₂O₃(氧化镓)是一种超宽禁带半导体材料,禁带宽度约 4.8 eV,具备高临界击穿场强、日盲探测能力与优异理化稳定性,在大功率电力电子与极端环境器件中极具应用潜力。相较于氮化铝、金刚石等材料,其熔体生长工艺在成本与速率上更具优势。随着缺陷选择性刻蚀技术成熟,晶体缺陷密度可被精准调控,有利于提升器件耐压性能。当前,β‑Ga₂O₃ 晶片尺寸从 4 英寸向 6 英寸扩展是产业化关键,直径提升 50% 可使晶片面积扩大 2.25 倍,便于兼容现有硅基产线。然而,传统 VB(垂直布里奇曼法)易开裂,EFG(导模法)受模具几何限制,难以制备高质量(100)斜切衬底。铸造法(casting method)由 VGF(垂直梯度凝固法)发展而来,无籽晶、无模具,可快速放大(100)晶向尺寸,应力小、可量产。该团队在铸造法基础上优化温场与自发结晶工艺,首次成功制备 6 英寸(100)晶面 Sn 掺杂与非故意掺杂 β‑Ga₂O₃ 单晶,并加工出同轴与 4° 偏角衬底,系统表征其结构、表面、光电及缺陷特性。

主要内容

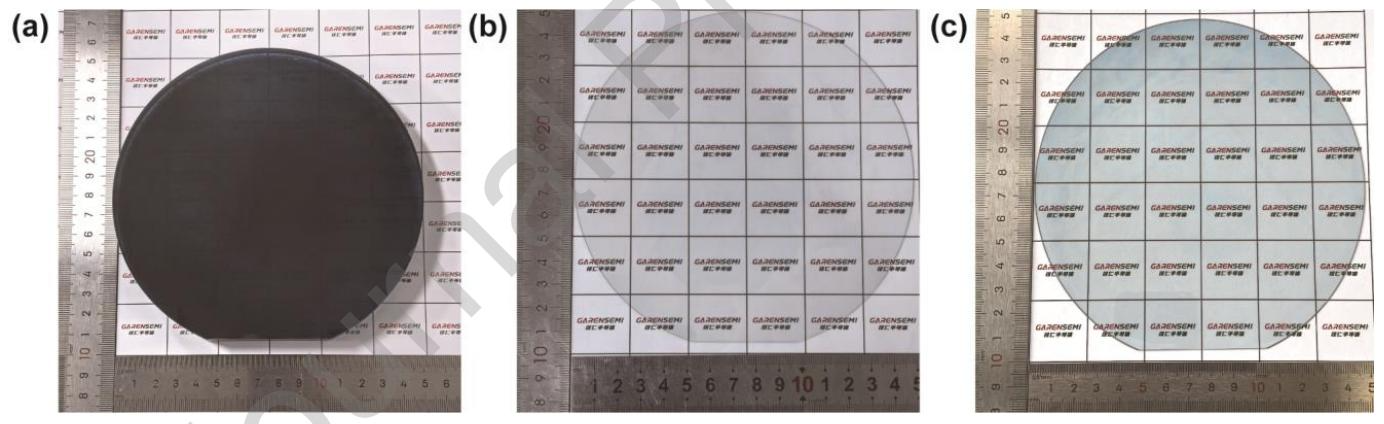

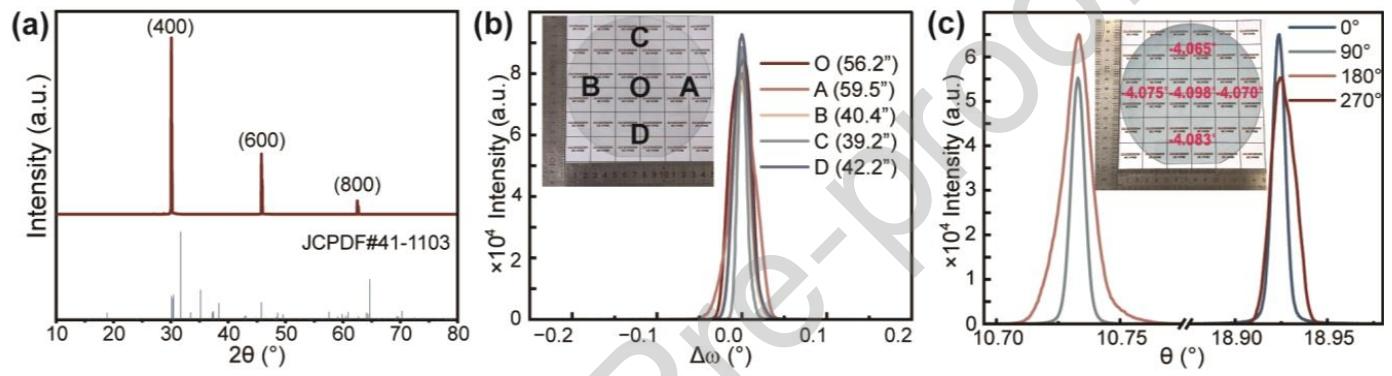

β‑Ga₂O₃ 作为面向大功率与极端环境电子应用的变革性超宽禁带半导体(Eg ~ 4.8 eV),将晶片尺寸从 4 英寸扩展至 6 英寸对其产业化至关重要。该工作通过优化铸造法在大尺寸 β‑Ga₂O₃ 晶体生长方面取得突破,首次成功制备 6 英寸 0.05 mol%(169 ppm wt)Sn 掺杂同轴与 4° 偏角(100)晶向晶片。综合表征显示其晶体质量优异:X 射线摇摆曲线半高宽 FWHM < 60 角秒,表面粗糙度 Ra < 0.2 nm,缺陷密度 ≤ 4×10³ cm⁻²,满足高性能同质外延生长的全部要求。铸造法通过控制自发结晶突破尺寸限制,同时保持优异的重复性与可扩展性。这些特性解决了 β‑Ga₂O₃ 商业化的关键障碍,可实现适用于高性能 MOSFET(金属氧化物半导体场效应晶体管)与 SBD(肖特基势垒二极管)的外延级与器件级衬底的晶片级制备。

创新点

1.尺寸突破:首次采用铸造法成功制备 6 英寸(100)晶面 β‑Ga₂O₃ 单晶,实现同轴与 4° 偏角衬底加工。

2.晶体质量优异:晶体摇摆曲线半高宽 < 60 角秒,表面粗糙度 Ra < 0.2 nm,位错密度 ≤ 4×10³ cm⁻²,满足外延要求。

3.工艺优势显著:无籽晶、无模具铸造法,降低结构应力,具备高重复性与工业可扩展性。

4.光电性能均匀:Sn 掺杂实现低电阻率与均匀载流子浓度,适配 MOSFET 与 SBD 器件制备。

结 论

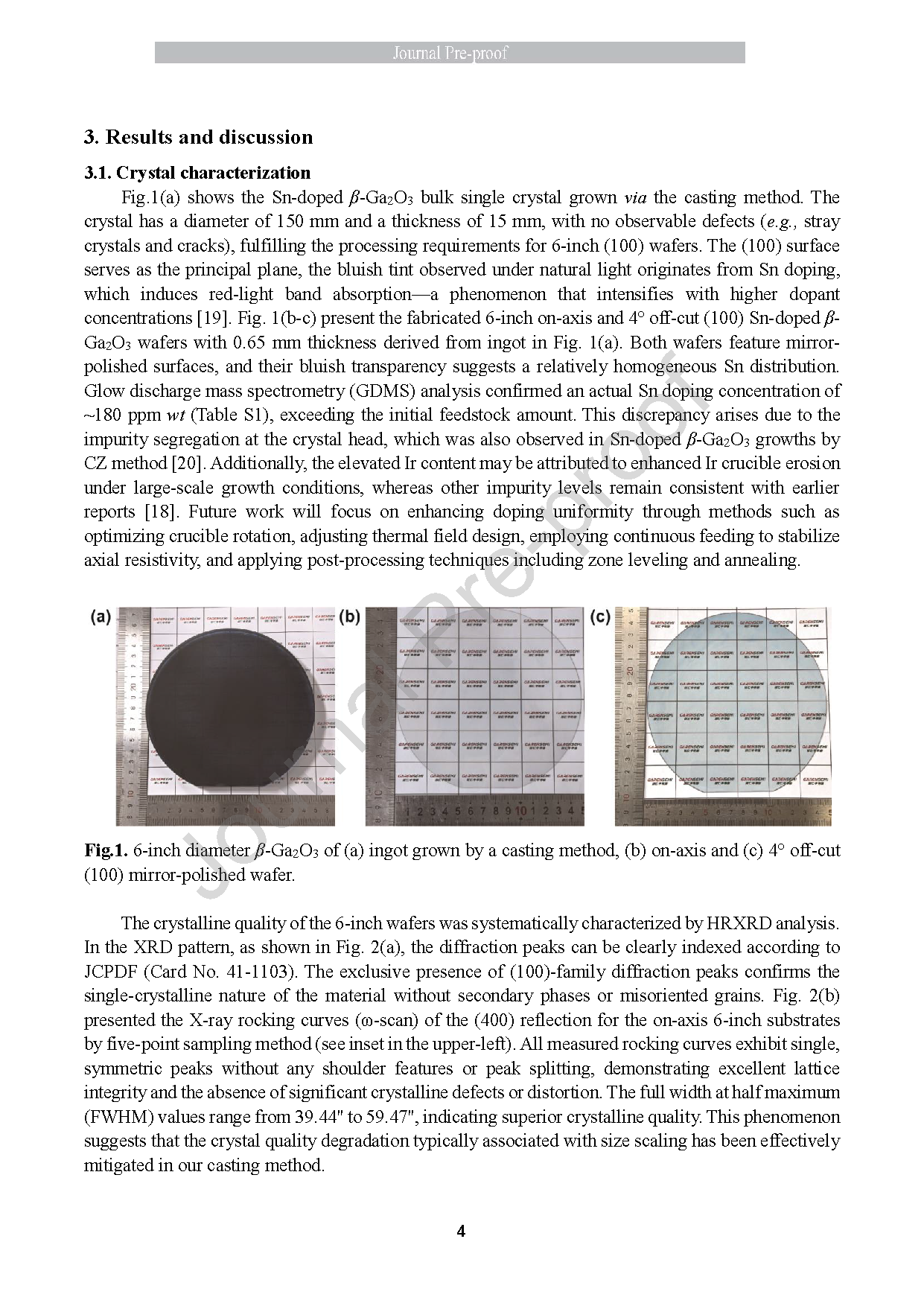

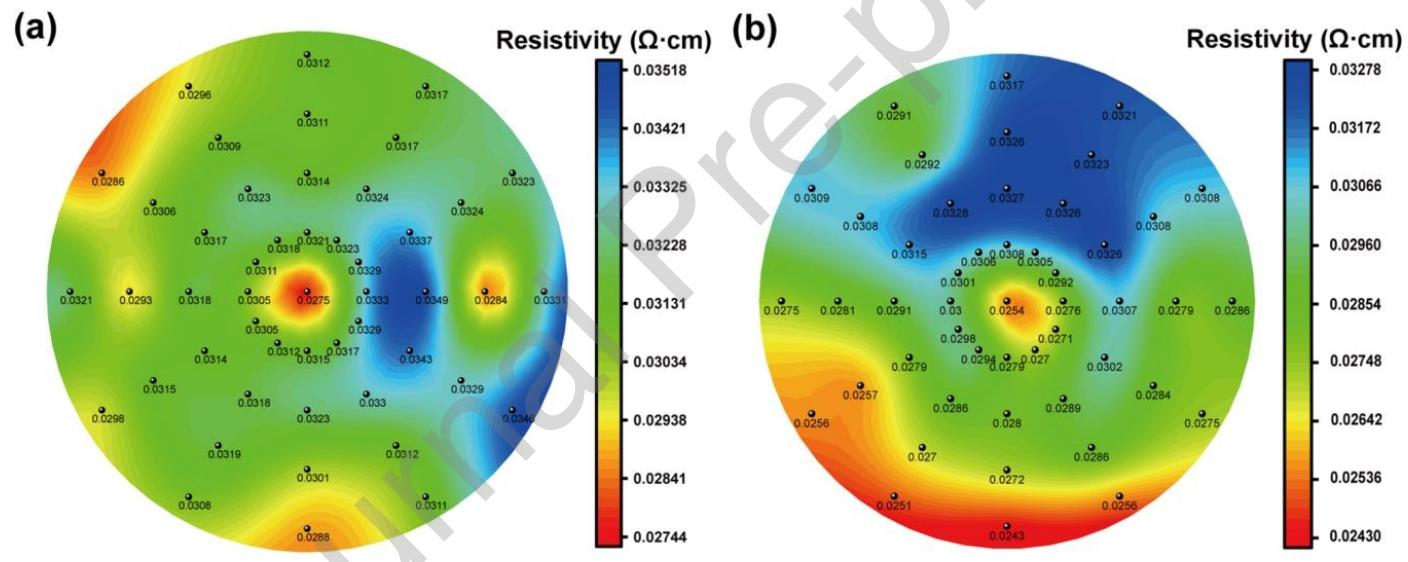

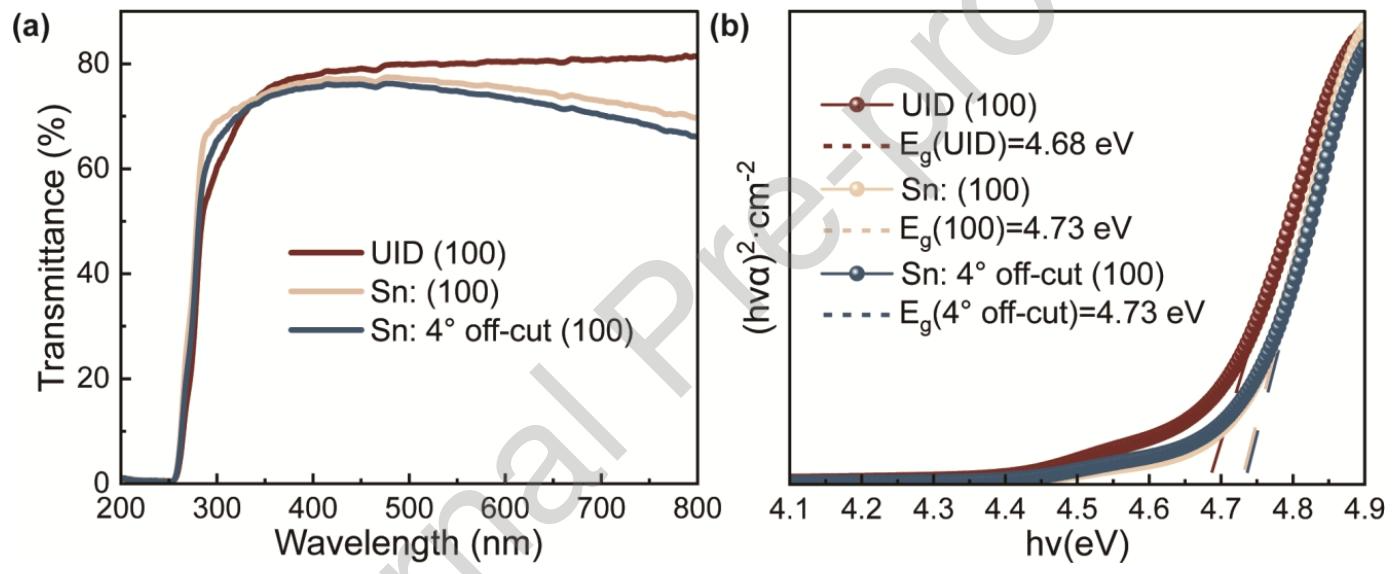

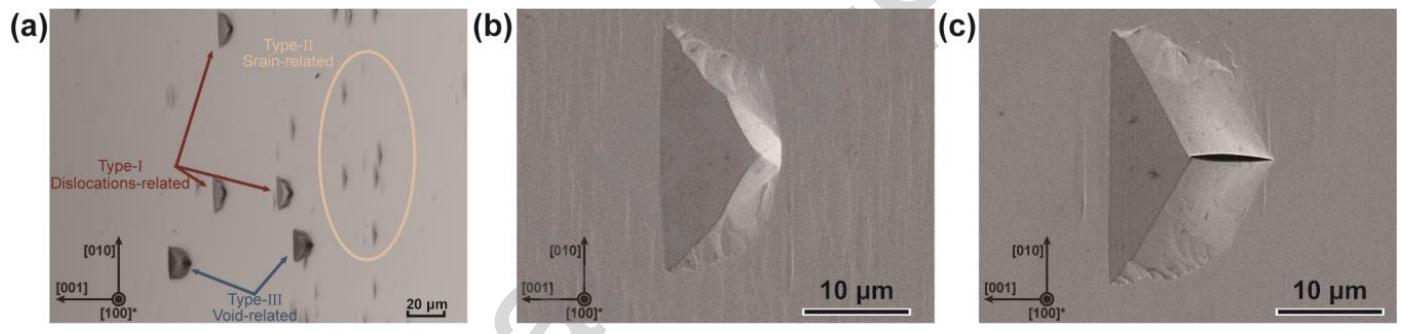

该团队采用铸造法成功生长 Sn 掺杂 6 英寸 β‑Ga₂O₃ 单晶,所获晶锭无杂晶、裂纹等宏观缺陷,质量优异。经精密加工得到同轴与精准 4° 偏角(100)晶面 β‑Ga₂O₃ 晶片,在大直径晶片制备上取得重要进展。全面表征表明,两类 6 英寸晶片均具备优异表面质量、厚度均匀性与平坦度,满足高质量同质外延生长的严苛要求。电学测试显示整片晶片电阻率稳定偏低(2×10-3 Ω·cm),适用于功率器件应用。化学刻蚀分析表明,同轴与偏角晶片位错密度相当(4×10³ cm⁻²),4° 偏角对缺陷形成影响可忽略;但 Sn 掺杂会使空洞缺陷密度高于非故意掺杂晶体,提示需进一步优化掺杂工艺。以上结果证实铸造法可规模化制备大直径 β‑Ga₂O₃ 材料,该工作开发的高质量外延级衬底为推动 β‑Ga₂O₃ 基电力电子与光电器件走向商业化奠定关键基础。

项目支持

该研究得到国家重点研发计划、国家自然科学基金、浙江省自然科学基金、国家高层次青年人才计划、杭州市领军型创新创业团队引进计划等项目资助。

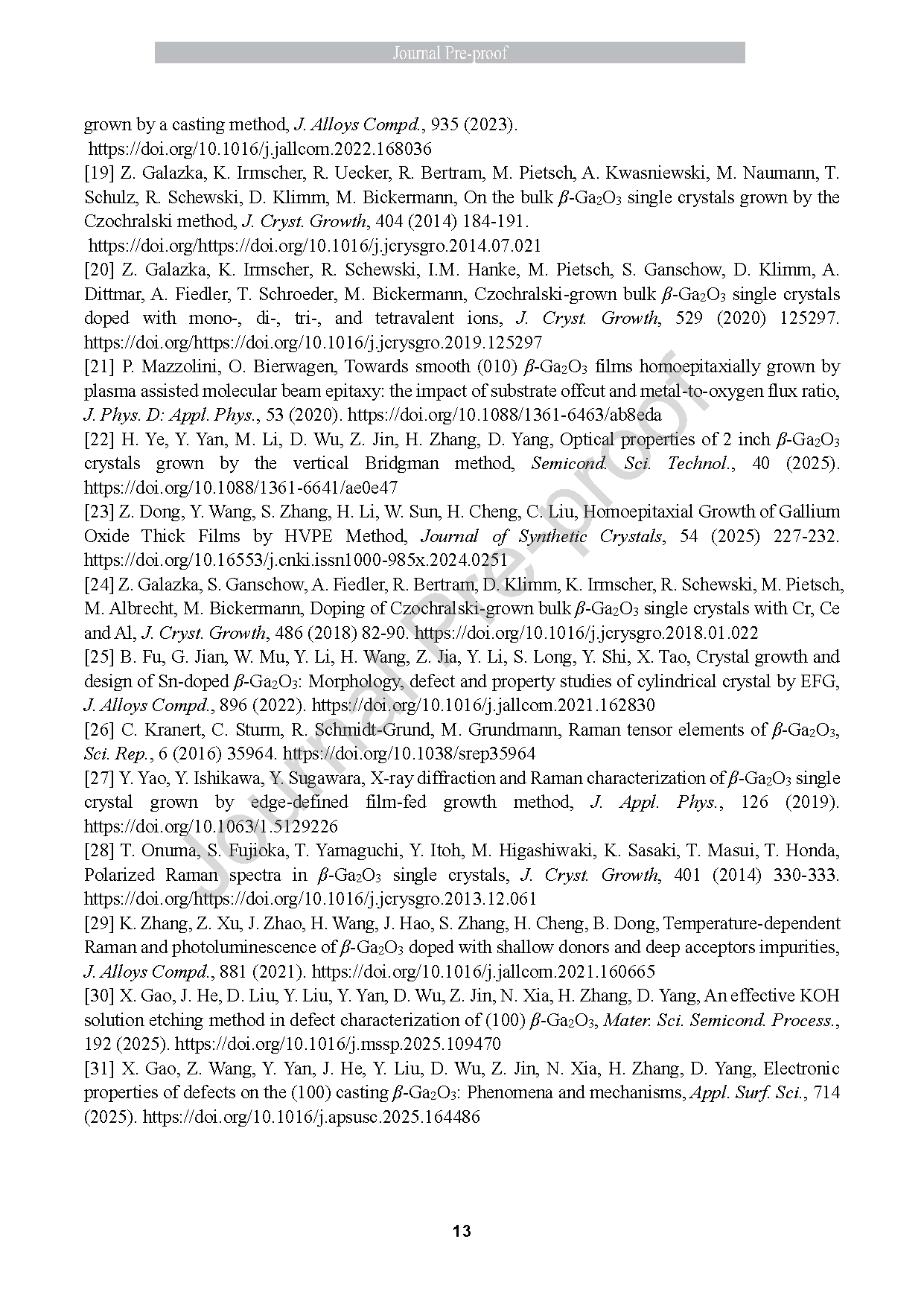

图 1. 铸造法制备的 6 英寸直径 β‑Ga₂O₃:(a) 晶锭,(b) 同轴与 (c) 4° 偏角(100)晶面抛光晶片。

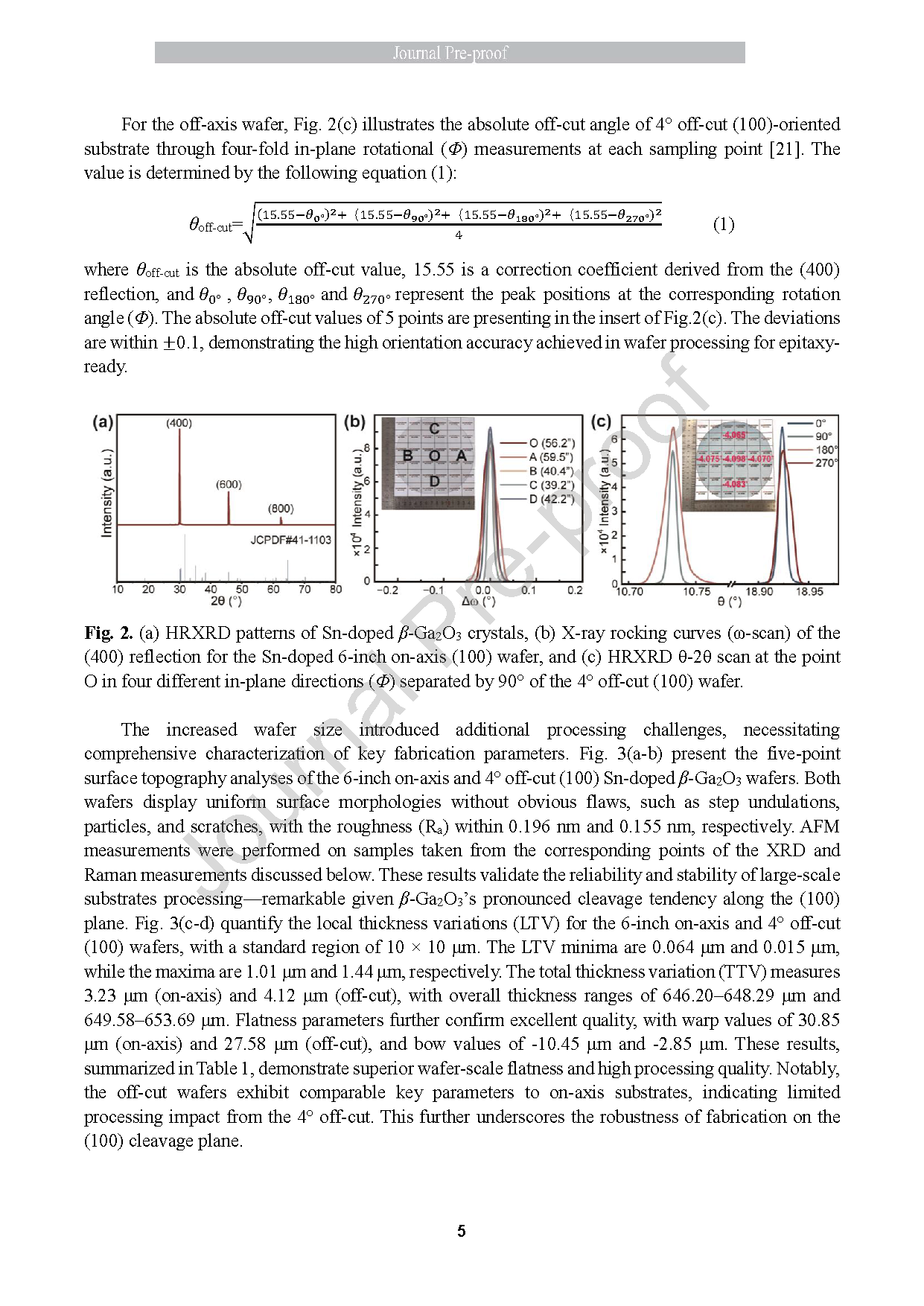

图 2. (a) Sn掺杂 β-Ga₂O₃晶体的高分辨 X 射线衍射(HRXRD)图谱;(b) Sn掺杂 6 英寸同轴 (100) 衬底(400)晶面的 X 射线摇摆曲线(ω 扫描);(c) 4° 偏角 (100) 衬底上 O 点在四个间隔 90° 的不同面内方向(Φ)上的高分辨 X 射线衍射 θ-2θ 扫描。

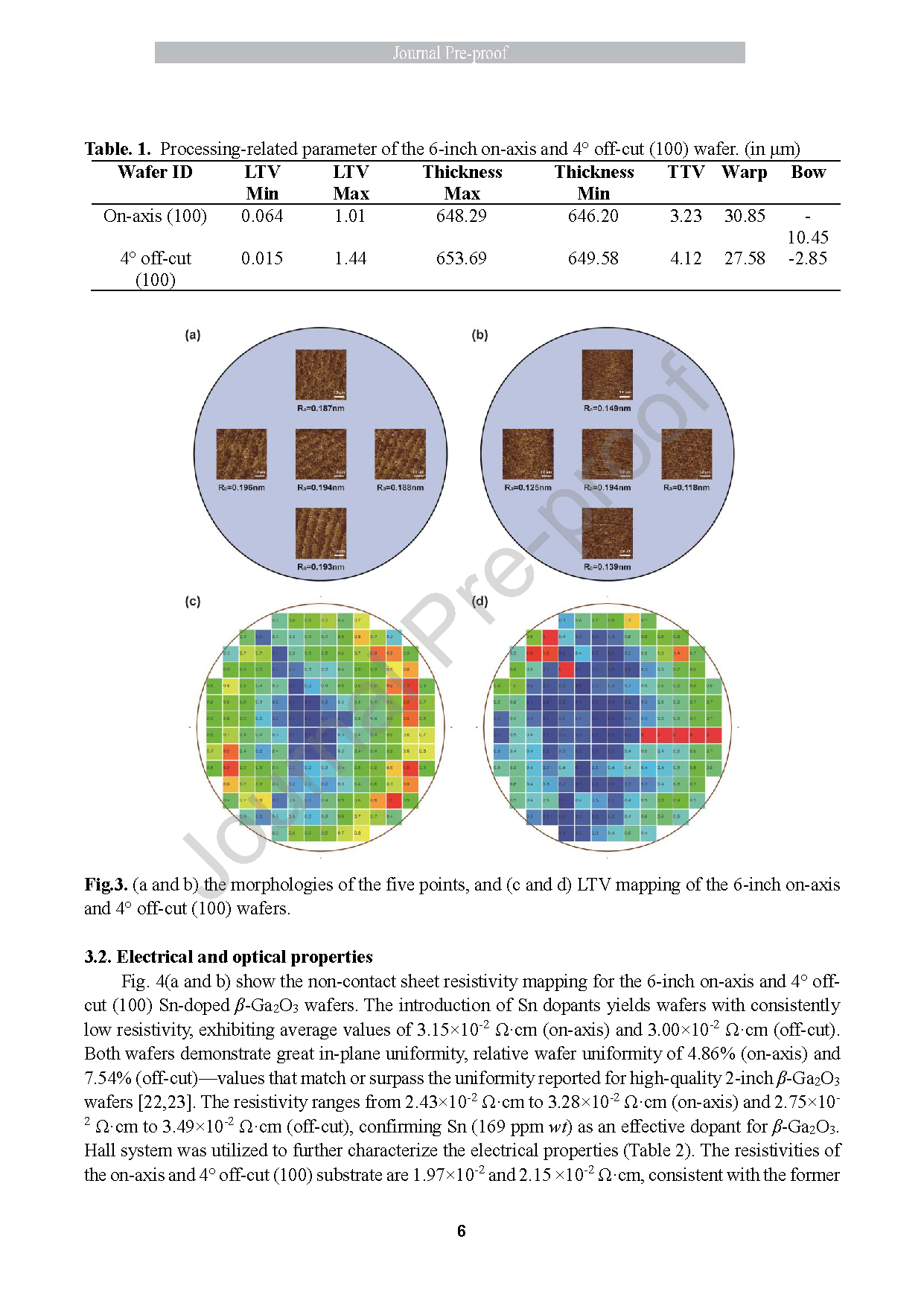

图 3. (a, b) 6 英寸同轴与 4° 偏角(100)晶片五点形貌;(c, d) 局部厚度变化(LTV)分布图。

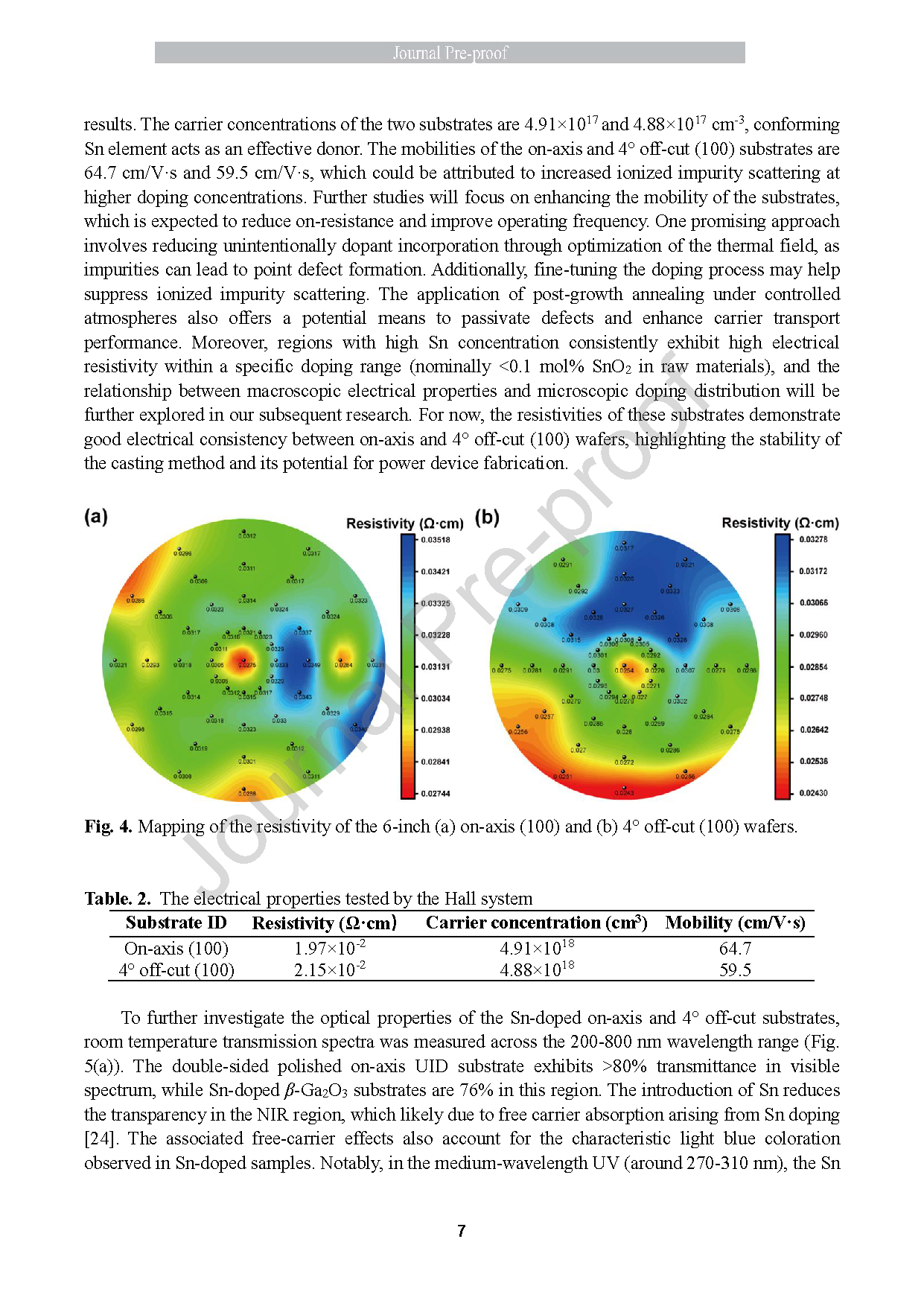

图 4. 6 英寸(a)同轴(100)与(b) 4° 偏角(100)晶片电阻率分布图。

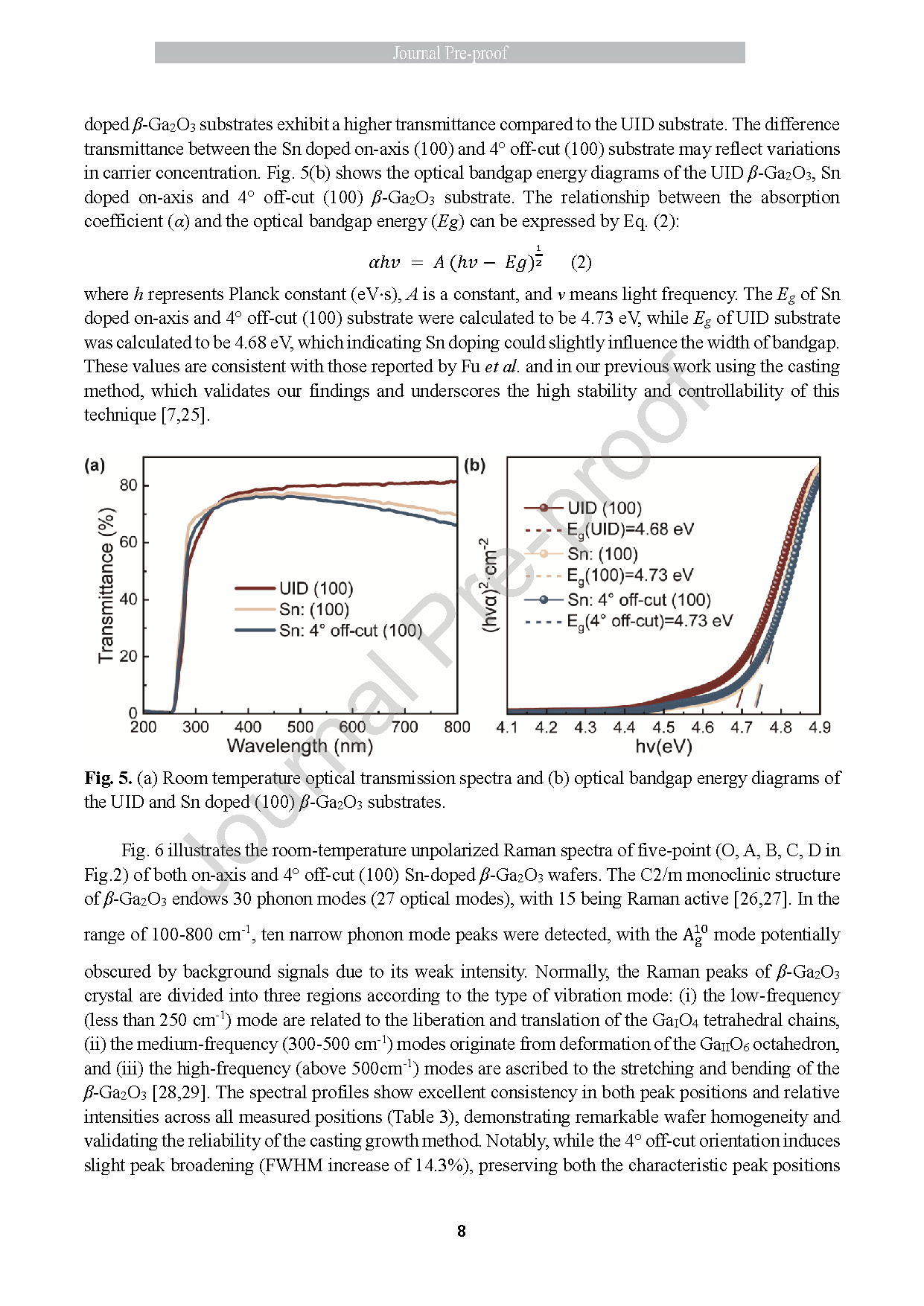

图 5. (a) 非故意掺杂与 Sn 掺杂(100)晶面 β‑Ga₂O₃ 衬底室温光学透射谱;(b) 光学禁带宽度图。

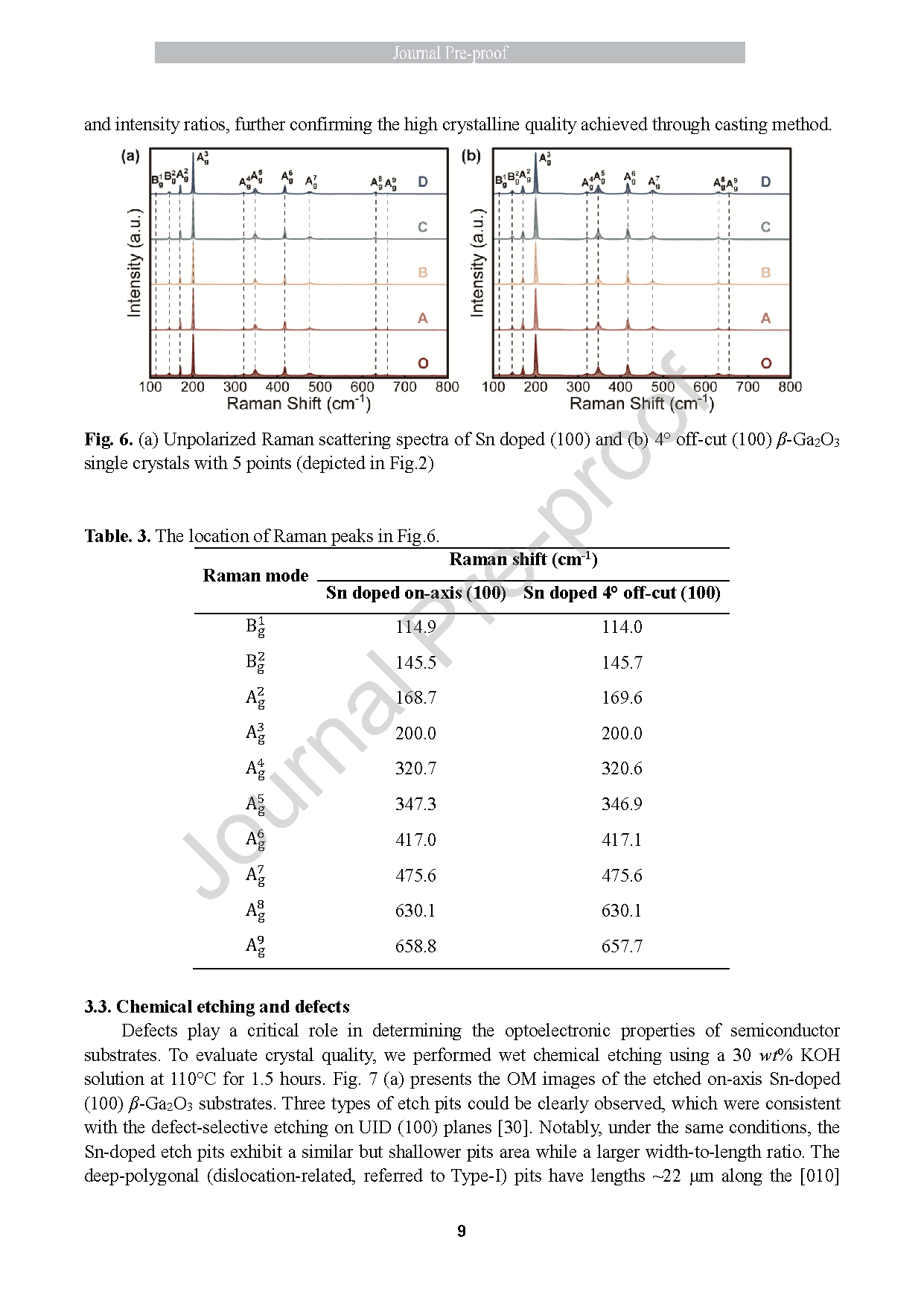

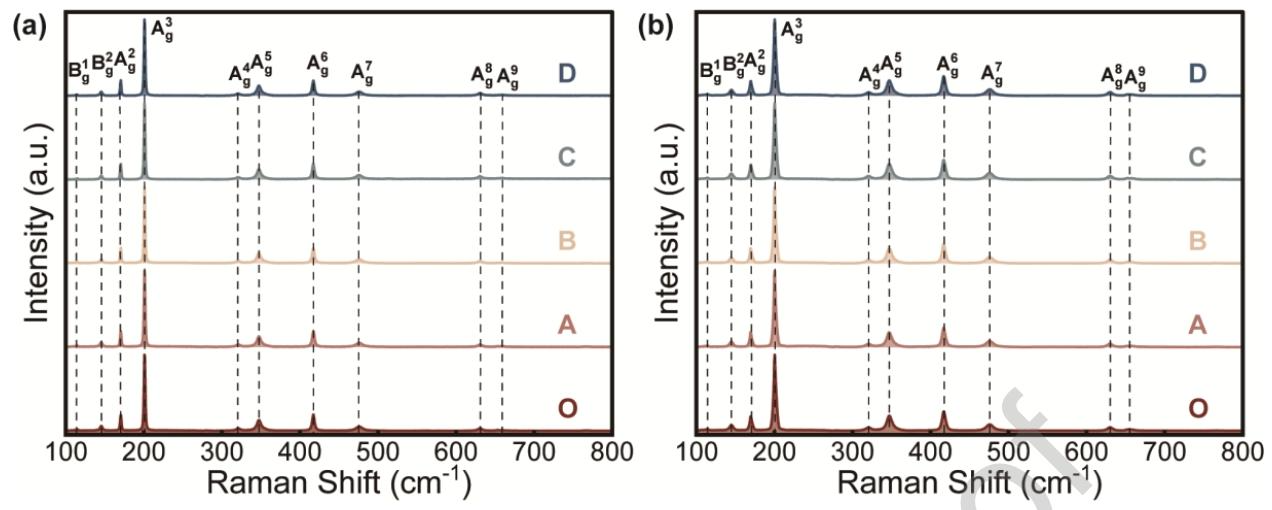

图 6. (a) Sn 掺杂(100)与(b) 4° 偏角(100)β‑Ga₂O₃ 单晶五点室温非偏振拉曼光谱。

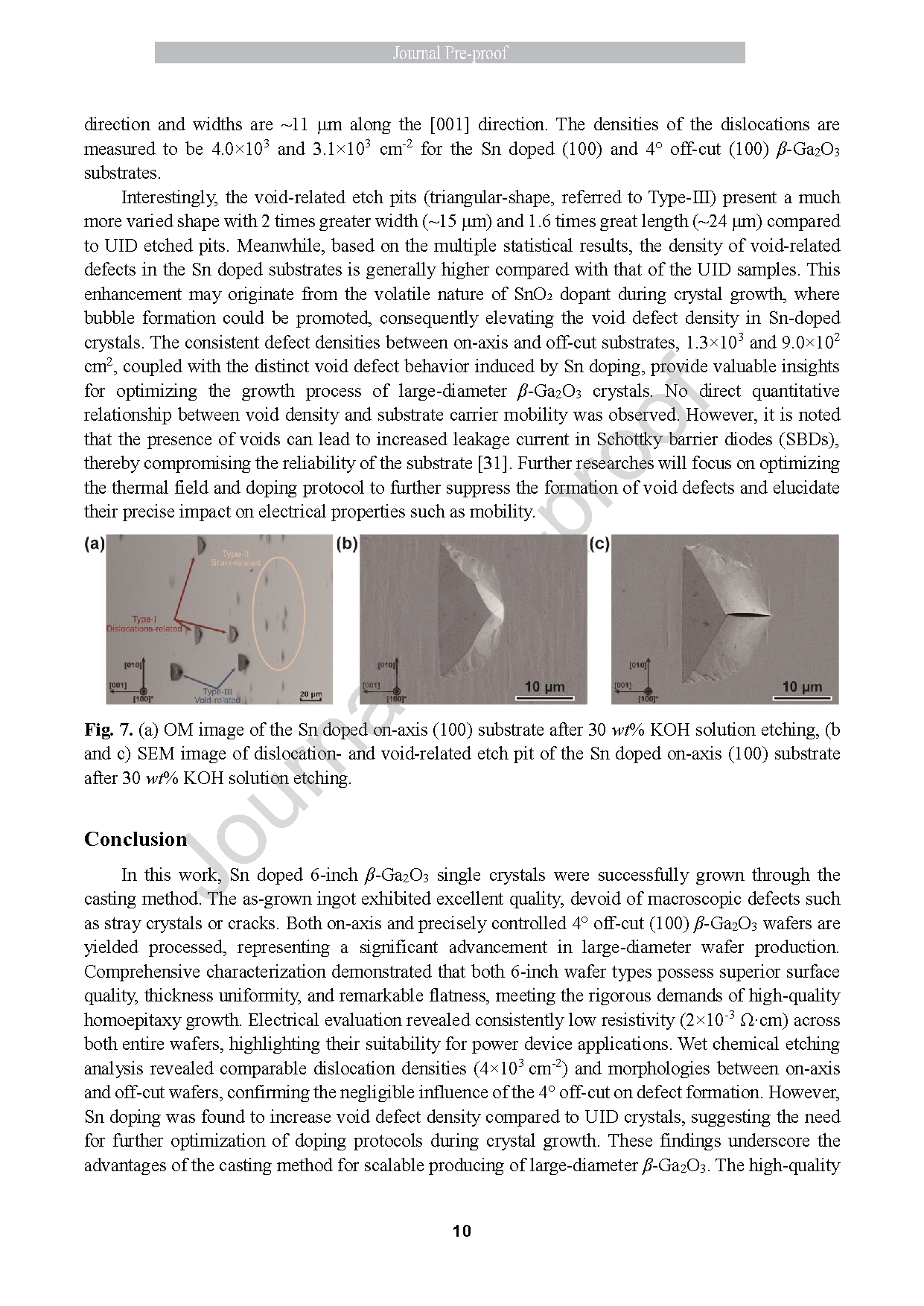

图 7. (a) Sn 掺杂同轴(100)衬底经 30 wt% KOH 溶液刻蚀后的光学显微镜图像;(b, c) 位错与空洞相关腐蚀坑的 SEM 图像。

DOI:

doi.org/10.1016/j.jallcom.2026.187699