【会员论文】电子科技大学:5.17 GW/cm² 高BFOM的2.7 kV新型3C-SiC/Ga₂O₃异质沟道E模式MISFET

日期:2025-11-10阅读:356

由电子科技大学易波副教授等人的研究团队在学术期刊 Microelectronics Journal 发布了一篇名为 A Novel 2.7 kV 3C-SiC/Ga2O3 Hetero-Channel E-mode MISFET With BFOM up to 5.17 GW/cm2(具有高达 5.17 GW/cm2 BFOM 的 2.7 kV 新型 3C-SiC/Ga2O3 异质沟道 E 模式 MISFET)的文章。

背 景

β-氧化镓(β-Ga2O3)因其超宽禁带和极高的击穿场强,被认为是下一代高功率电子器件的理想材料。然而,β-Ga2O3 的规模化应用面临两大核心瓶颈,极低的热导率会导致器件在高功率运行时产生严重的自热效应,限制了其可靠性。较低的沟道迁移率会导致器件的导通电阻偏高,增加了功率损耗。相比之下,碳化硅(SiC),特别是 3C-SiC 相,具有优异的热导率和高电子迁移率,但在击穿场强方面不及 Ga2O3。因此,如何将 Ga2O3 的高耐压特性与 SiC 的高迁移率、高导热性相结合,是突破当前技术瓶颈的关键。

主要内容

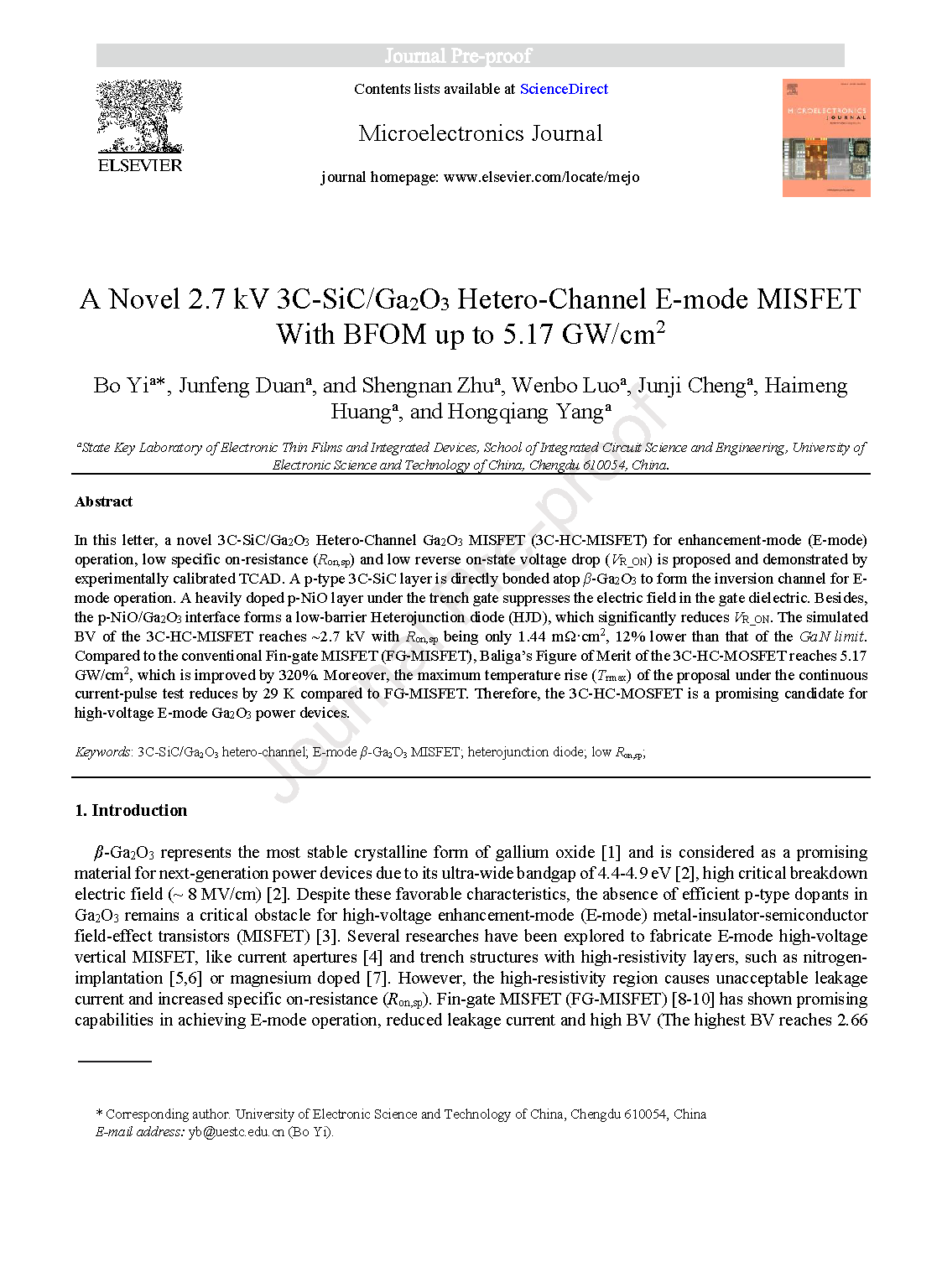

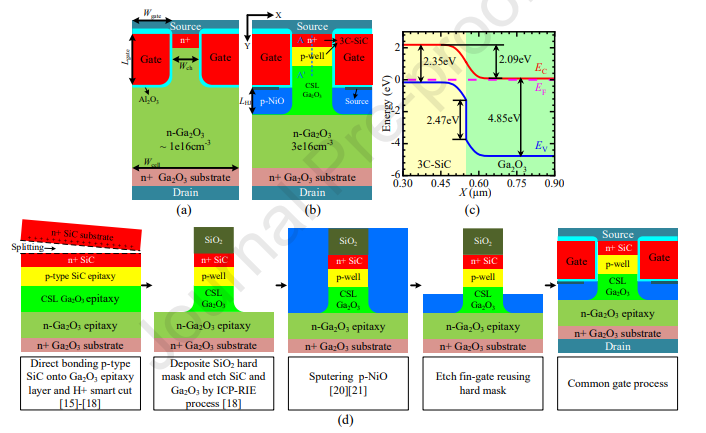

本文提出一种新型 3C-SiC/Ga2O3 异质沟道 Ga2O3 金属绝缘层场效应晶体管(3C-HC-MISFET),通过实验校准的 TCAD 技术实现增强模式(E-mode)工作,具有低特定导通电阻(Ron,sp)和低反向导通状态电压降(VR_ON)特性。通过将 p 型 3C-SiC 层直接键合于 β-Ga2O3 之上,形成增强模式工作的反转通道。沟槽栅下方的重掺杂 p-NiO 层有效抑制了栅极介质中的电场。此外,p-NiO/Ga2O3 界面形成低势垒异质结二极管(HJD),显著降低 VR_ON。模拟结果表明,该 3C-HC-MISFET 的击穿电压(BV)达约 2.7 kV,开路电阻 Ron,sp 仅为 1.44 mΩ·cm2,较 GaN 极限值降低 12%。相较于传统 Fin 栅金属氧化物半导体场效应晶体管(FG-MISFET),3C-HC-MOSFET 的巴利加优值达 5.17 GW/cm2,提升幅度达 320%。在连续电流脉冲测试中,该器件的最大温升(Trmax)较 FG-MISFET 降低 29 K。因此,3C-HC-MOSFET 是高压 E 模式 Ga2O3 功率器件的理想候选方案。

创新点

● 提出了将 3C-SiC 和 β-Ga2O3 结合用于沟道层的新型器件结构,成功将两种材料的优势集于一体。

● 该设计有效克服了 Ga2O3 材料本身低迁移率和低热导率的固有缺点,显著提升了器件的综合性能。

● 仿真得到的 BFOM 远超现有报道的 Ga2O3 器件,为超宽禁带半导体功率器件的设计提供了全新的思路。

结 论

本文提出了一种新型高压 E-mode Ga2O3 金属绝缘层场效应晶体管(MISFET),其静态导通电阻 Ron,sp 极低,突破了 GaN 材料的极限。采用高沟道迁移率的 3C-SiC 层作为沟道区域,并在栅极底部设置 p 型 NiO 层以保护栅氧化层 Al2O3 和 3C-SiC 层免受预击穿损伤,从而提升了击穿电压(BV)和器件可靠性。相较于 FG-MISFET,3C-HC-MISFET 实现 5.17 GW/cm2 的高比功耗电流密度(BFOM),较 GaN 极限值提升 12%。其导通电压降低 2.33 V。此外,3C-HC-MISFET 的电流-电压曲线漂移显著缩短。更值得注意的是,正向与反向导通状态下的最大温升分别降低 29 K 和 33 K。这些特性使其成为未来高性能电力电子应用的理想候选器件。

图1. FG-MISFET与3C-HC-MISFET的示意性截面图。沟槽 Ga2O3 的圆角半径设定为 0.2 μm。(a) FG-MISFET。(b) 3C-HC-MISFET。(c) 图1 (b) 中 AA' 方向的能带图。(d) 3C-HC-MISFET 的可能制备工艺流程。

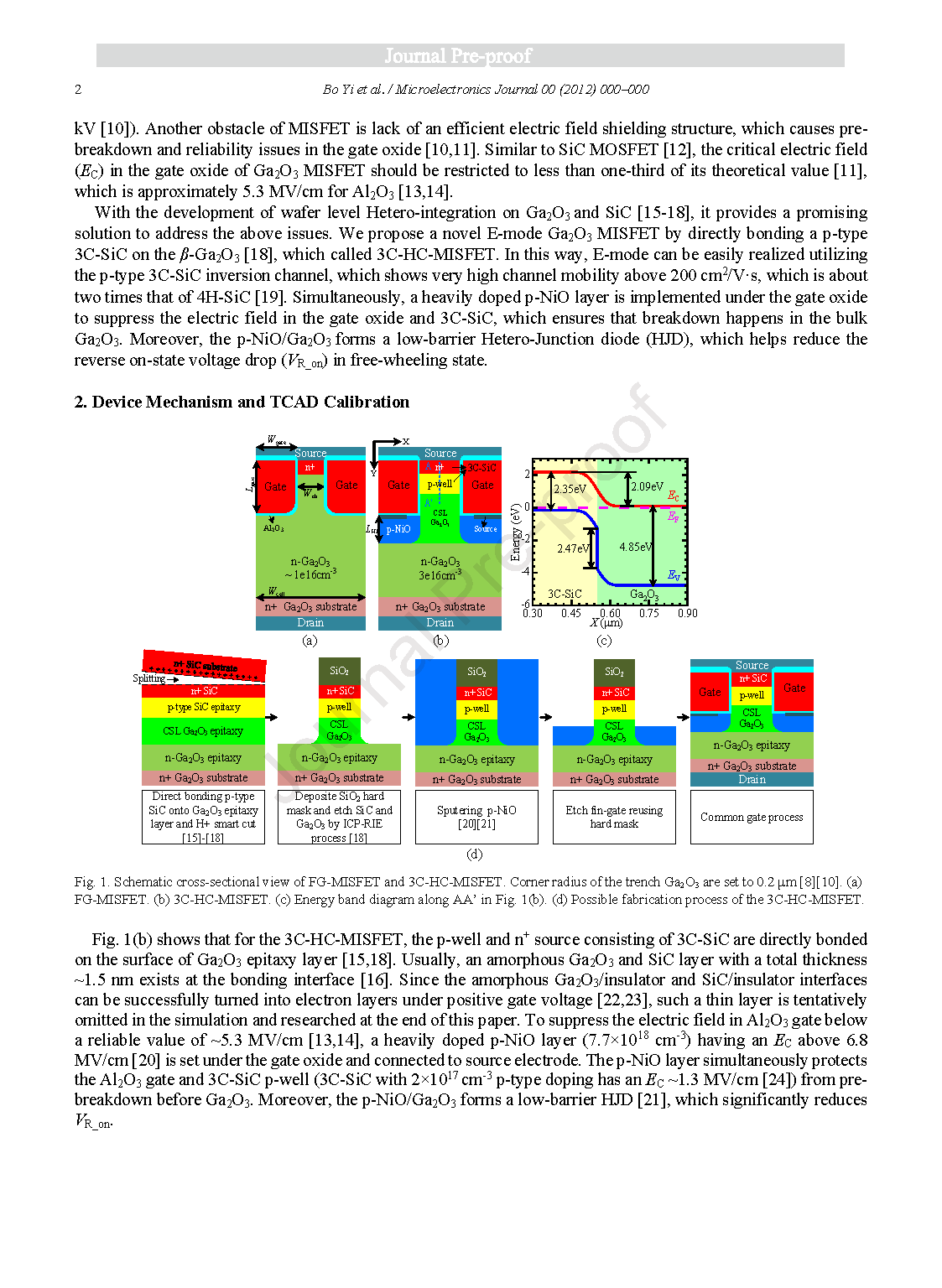

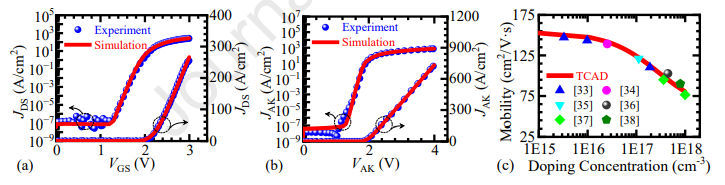

图2. 基于测量数据的参数与模型校准。(a)FG-MISFET 的对数与线性标度校准。(b)p-NiO/Ga2O3 异质结的对数与线性标度校准。(c)Arora 迁移率模型的校准。

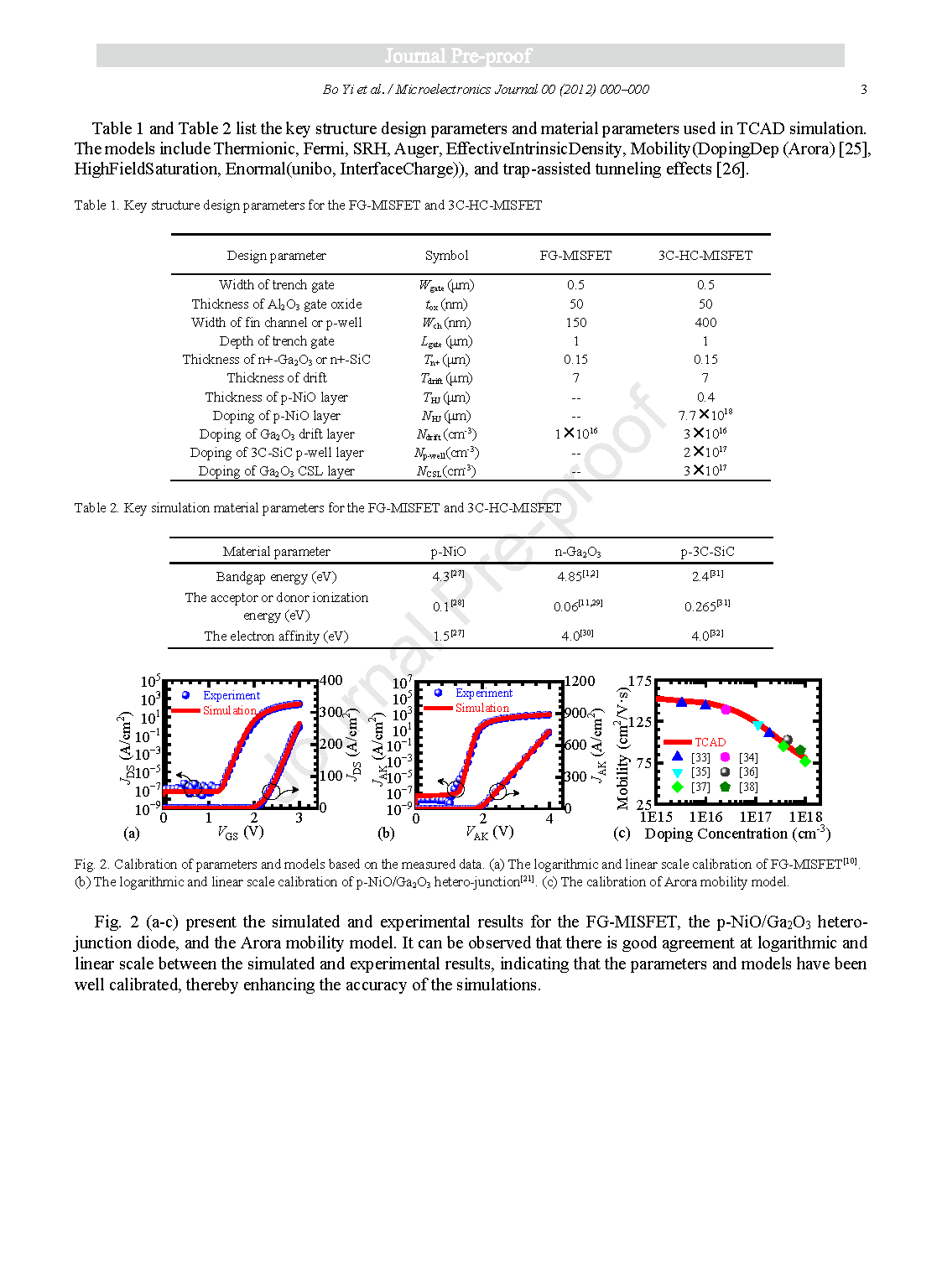

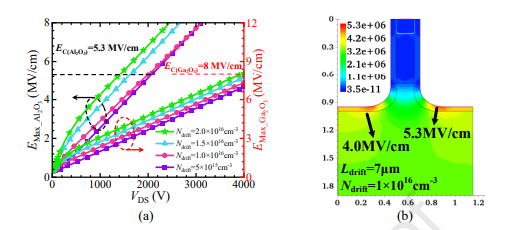

图3. FG-MISFET中不同材料的最大电场强度(Emax)。(a)Ndrift对Al2O3和Ga2O3的Emax的影响。(b)当BV=2000 V、Ndrift=1×10¹⁶ cm⁻³时的电场分布。

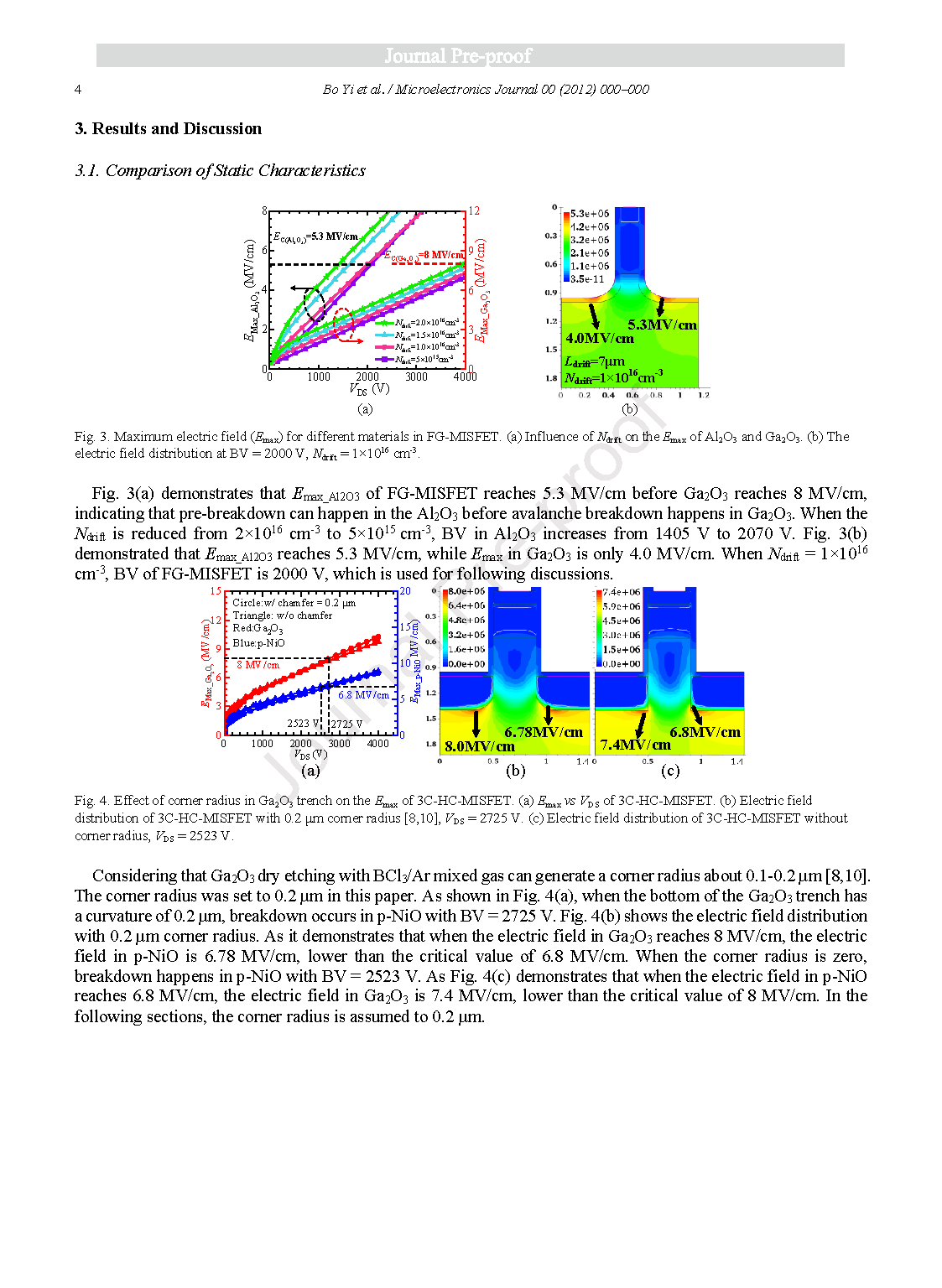

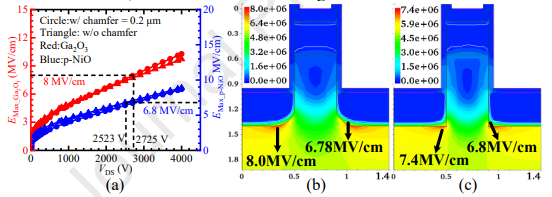

图4. Ga2O3沟槽圆角半径对 3C-HC-MISFET Emax 的影响。(a) Emax 与 VDS 关系曲线。(b) 0.2 μm 角半径 3C-HC-MISFET在 VDS=2725 V 时的电场分布。(c) 无角半径 3C-HC-MISFET 在 VDS=2523 V 时的电场分布。

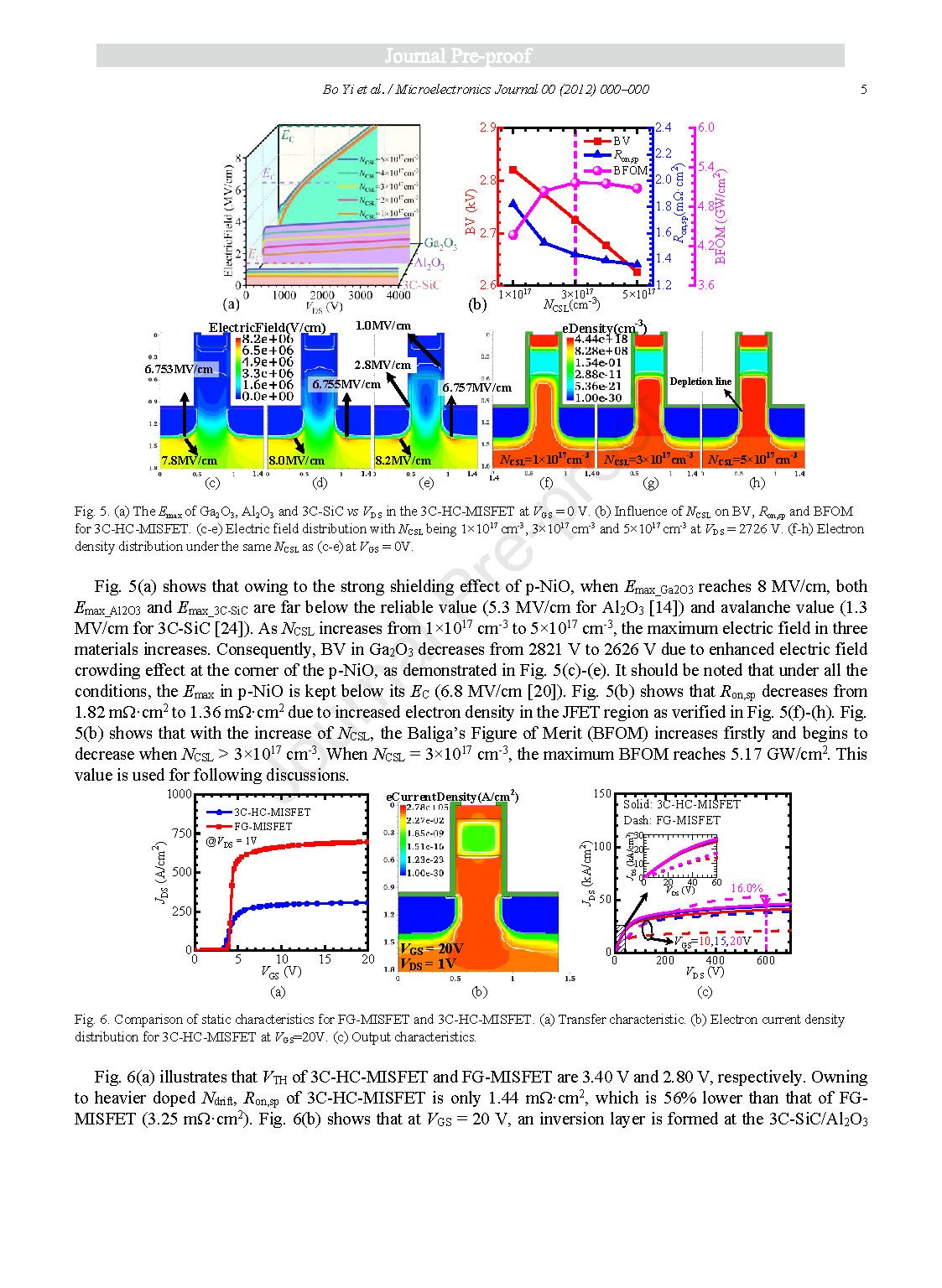

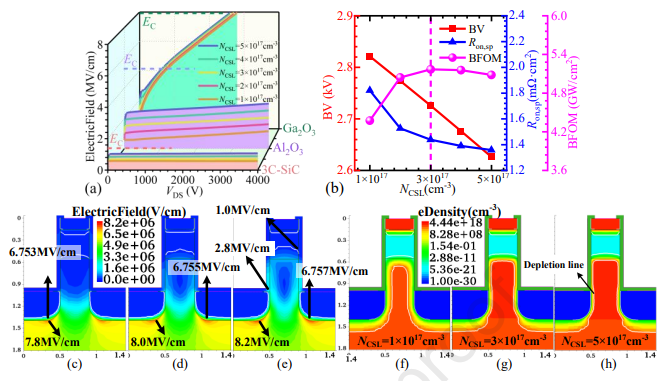

图5. (a) 在VGS=0 V 时,3C-HC-MISFET 中 Ga2O3、Al2O3 和 3C-SiC 的 Emax 随 VDS 变化曲线。(b) NCSL 对 3C-HC-MISFET 的 BV、Ron,sp 和 BFOM 的影响。(c-e) 当 NCSL 分别为 1×1017 cm-3、3×1017 cm-3 和 5×1017 cm-3 时,在 VDS=2726 V 下的电场分布。(f-h) 在与 (c-e) 相同 NCSL 条件下,VGS=0 V 时的电子密度分布。

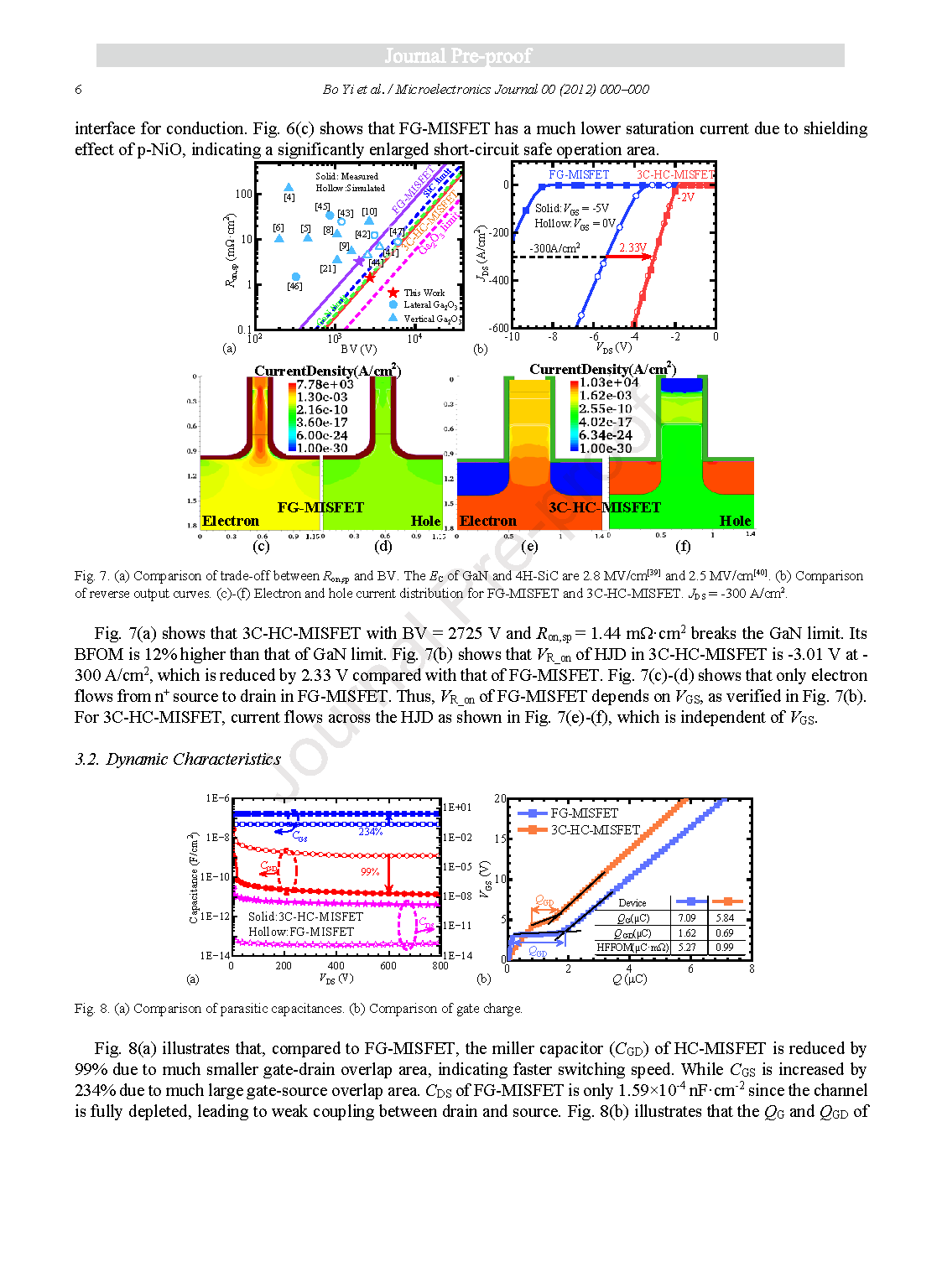

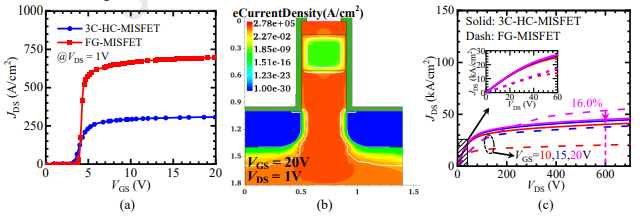

图6. FG-MISFET 与 3C-HC-MISFET 静态特性对比。(a)传输特性。(b)VGS=20 V 时 3C-HC-MISFET 的电子电流密度分布。(c)输出特性。

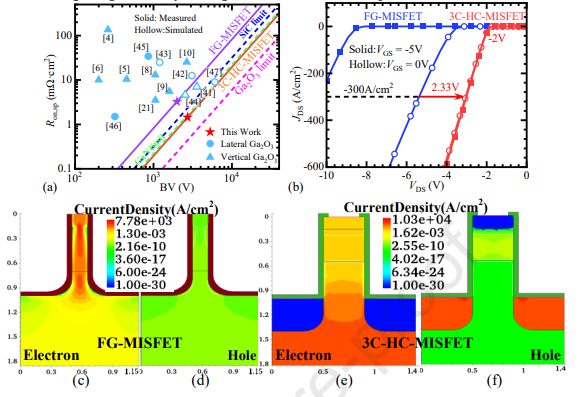

图7. (a) GaN 与 4H-SiC 的 Ron,sp 与击穿电压(BV)折衷特性对比。GaN 与 4H-SiC 的电导率分别为 2.8 MV/cm 和 2.5 MV/cm。(b) 反向输出曲线对比。(c)-(f) FG-MISFET 与 3C-HC-MISFET 的电子与空穴电流分布。JDS = -300 A/cm2。

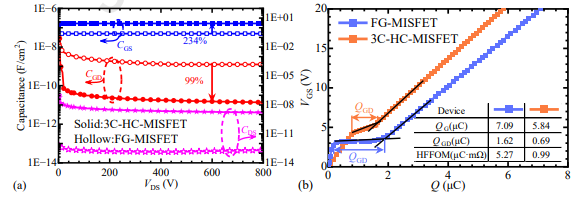

图8. (a) 寄生电容比较。 (b) 栅极电荷比较。

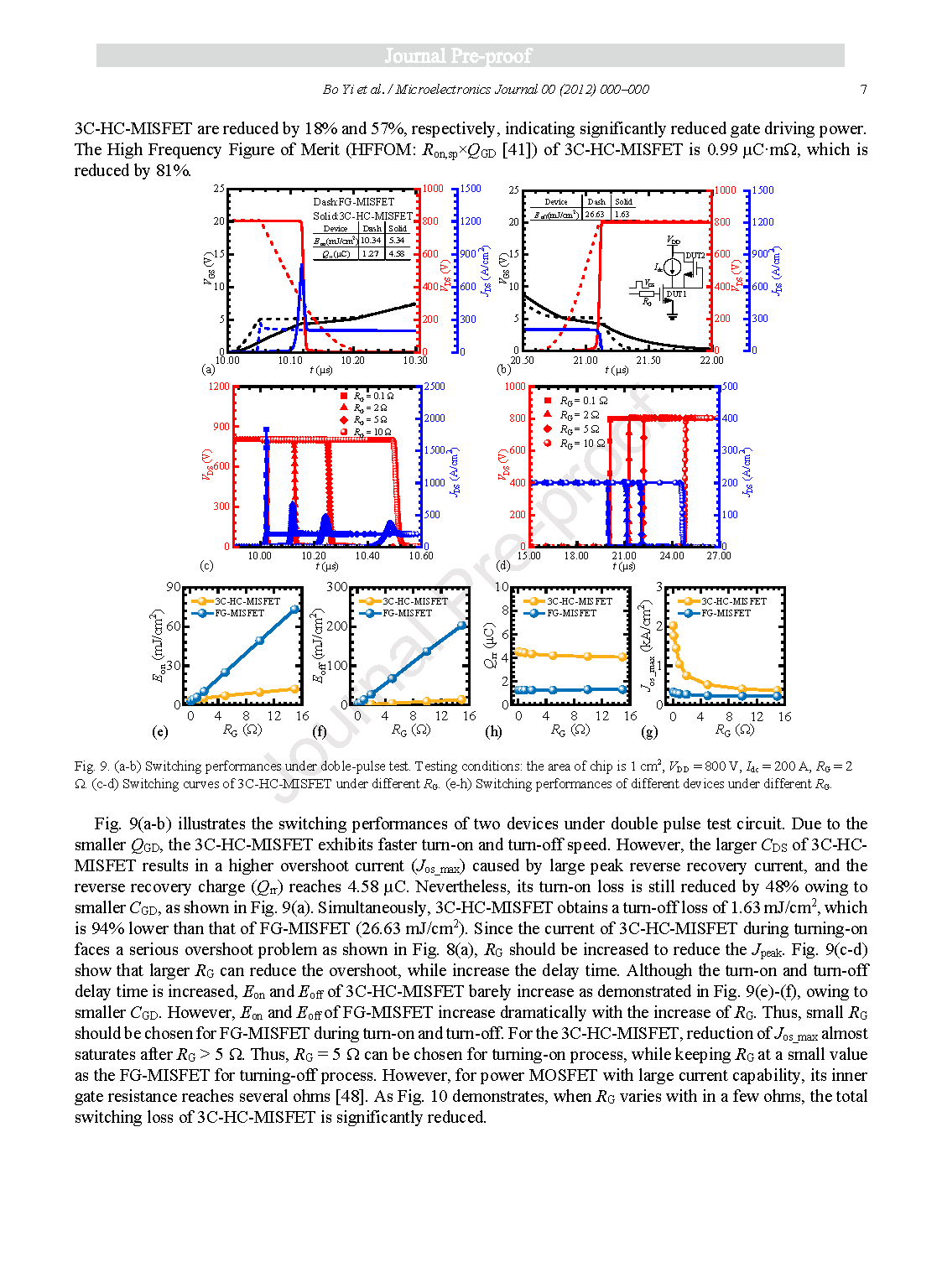

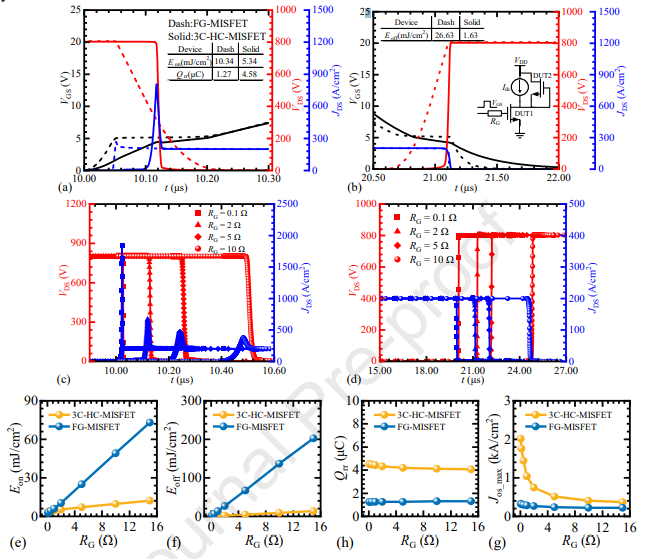

图9. (a-b) 双脉冲测试下的开关性能。测试条件:芯片面积为 1 cm2,VDD = 800 V,Idc = 200 A,RG = 2 Ω。(c-d) 不同 RG 条件下 3C-HC-MISFET 的开关曲线。(e-h) 不同器件在不同 RG 条件下的开关性能。

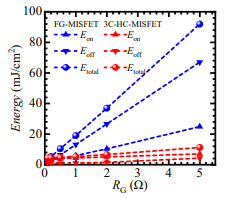

图10. 不同 RG 条件下 3C-HC-MISFET 的开关损耗。

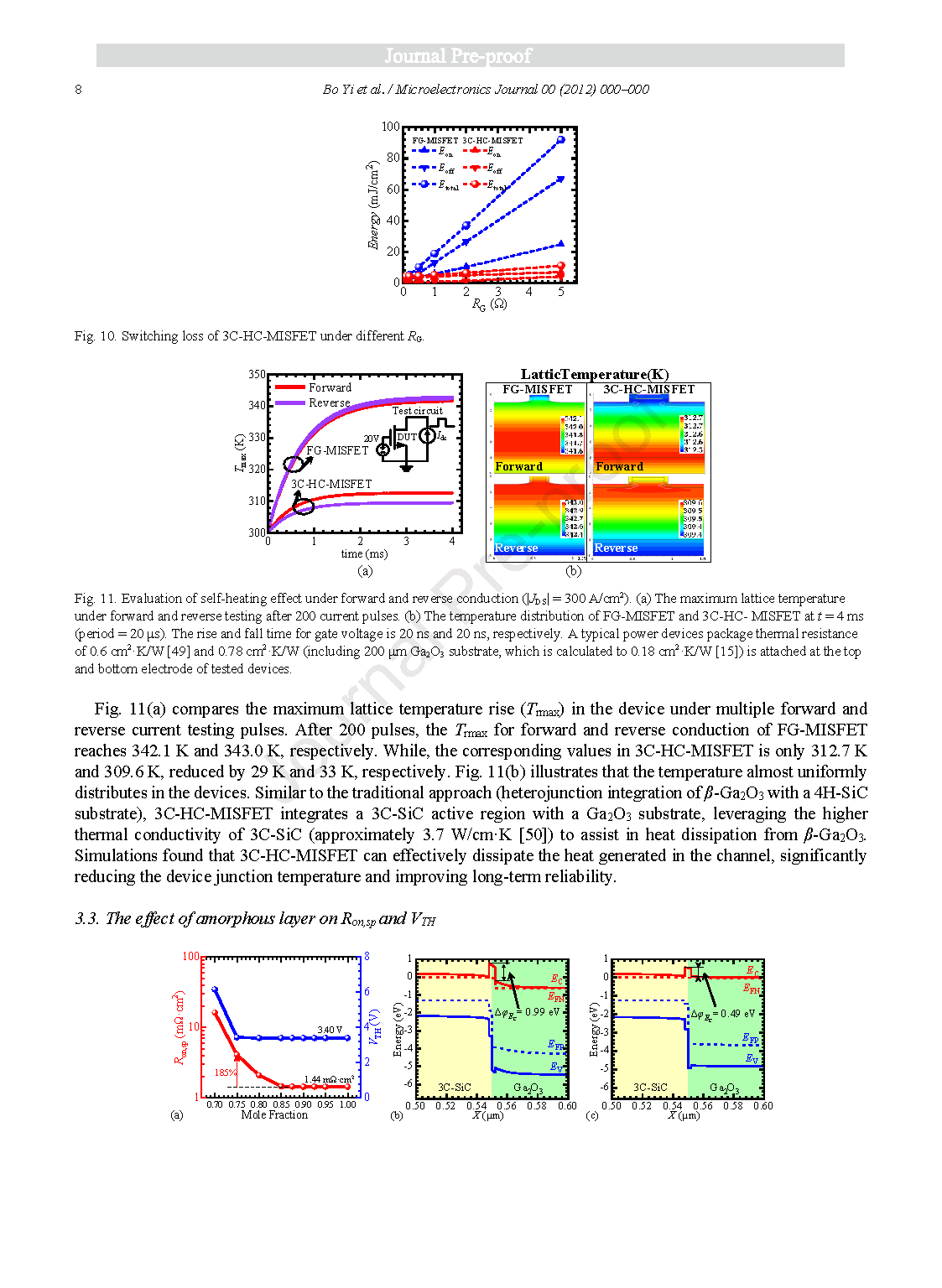

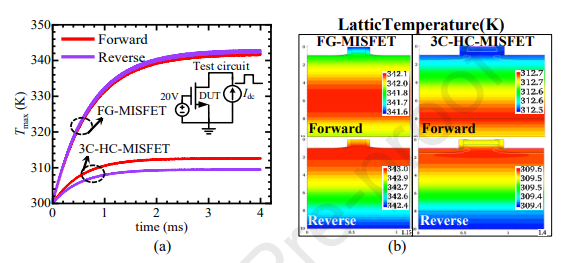

图11. 正向与反向导通条件下自发热效应评估(|JDS| = 300 A/cm2)。(a) 经 200 次电流脉冲测试后正反向测试的最高晶格温度。(b) t = 4 ms(周期 = 20 μs)时 FG-MISFET 与 3C-HC-MISFET 的温度分布。栅极电压上升/下降时间分别为 20 ns。测试器件上下电极分别贴附典型功率器件封装热阻 0.6 cm2·K/W 与 0.78 cm2·K/W(含200 μm Ga2O3 衬底,其热阻计算值为 0.18 cm2·K/W)。

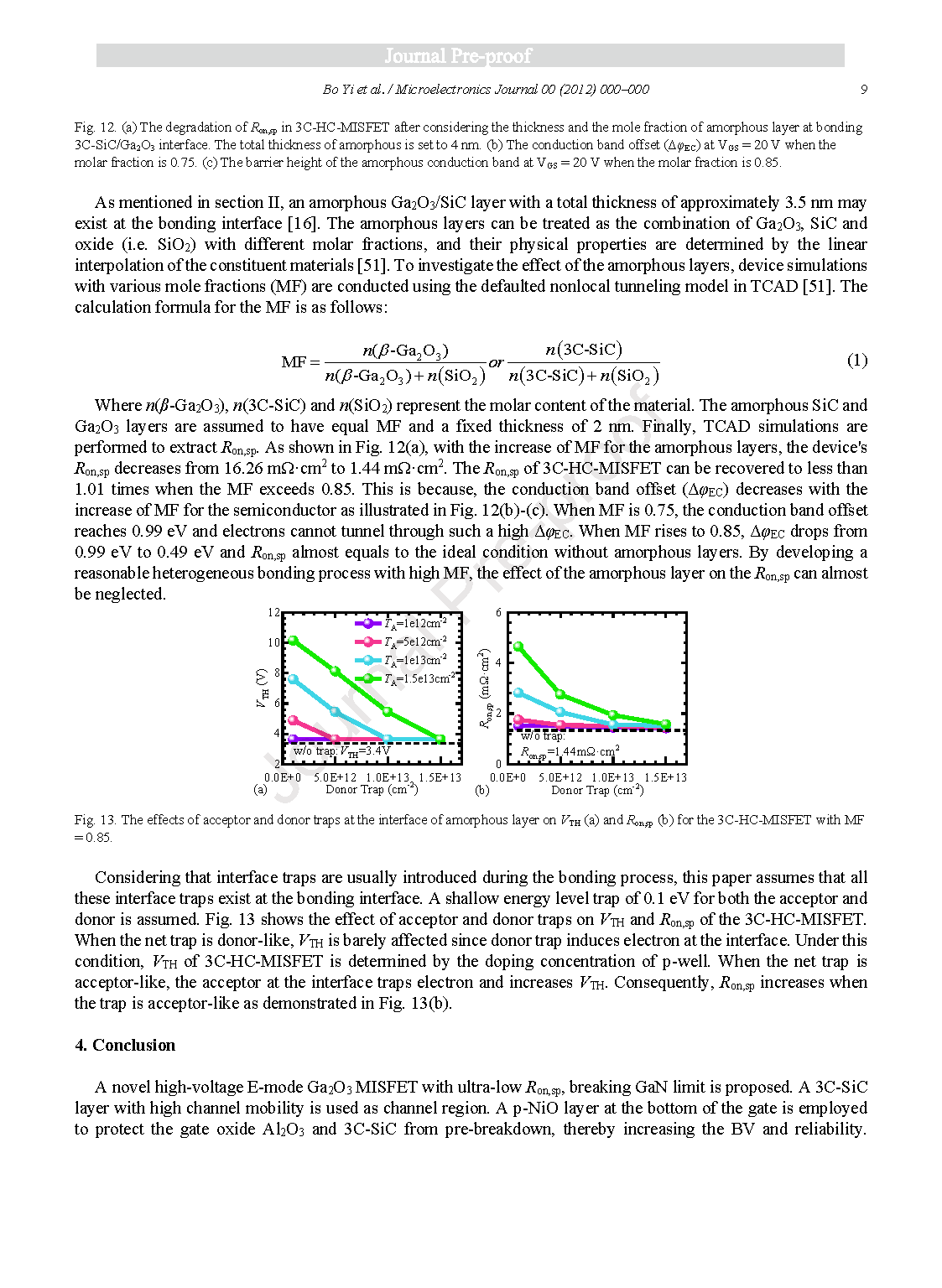

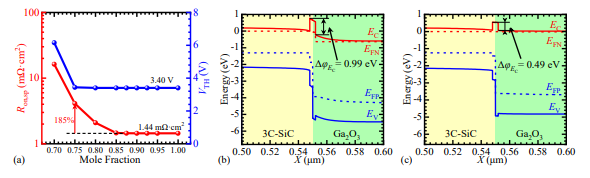

图12. (a) 考虑键合 3C-SiC/Ga2O3 界面处非晶层厚度与摩尔分数后,3C-HC-MISFET中 Ron,sp 的退化现象。非晶层总厚度设定为 4 nm。(b) 当摩尔分数为 0.75 时,在 VGS=20 V 条件下的导带偏移量(ΔφEC)。(c) 当摩尔分数为 0.85 时,在 VGS=20 V 条件下非晶导带的势垒高度。

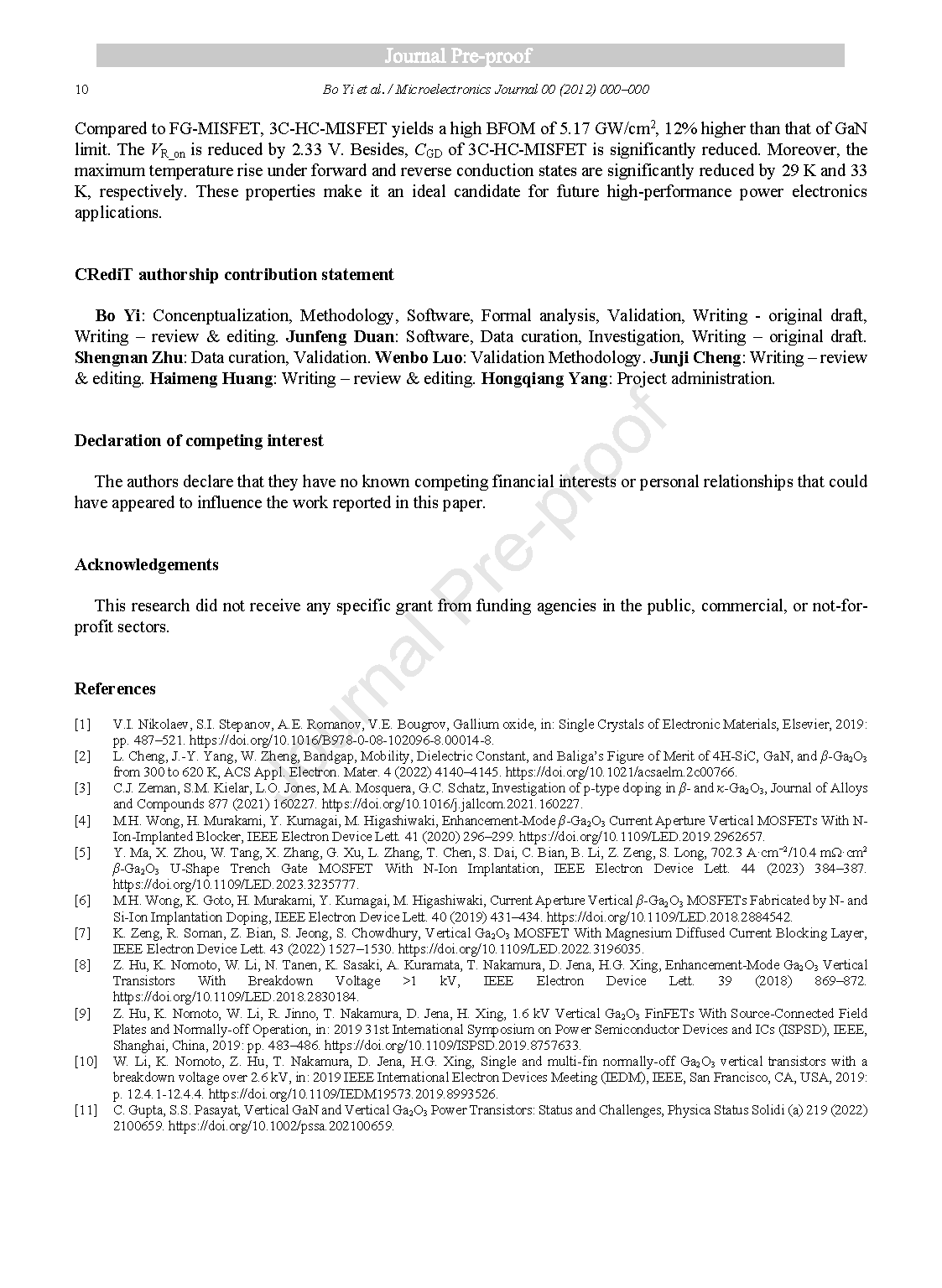

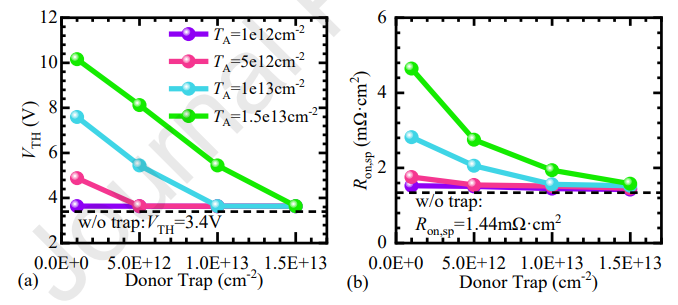

图13. 对于 MF=0.85 的 3C-HC-MISFET,非晶层界面处受主和施主陷阱对 VTH(a)和 Ron,sp(b)的影响。

DOI:

doi.org/10.1016/j.mejo.2025.106955