【会员论文】APL丨中科大龙世兵教授&中科院纳米所张晓东研究员团队:通过HF侧壁处理实现214 MWcm²垂直 β-Ga₂O₃ UMOSFET

日期:2026-02-28阅读:237

由中国科学技术大学龙世兵教授、徐光伟研究员、周选择博士&中国科学院苏州纳米技术与纳米仿生研究所张晓东研究员的研究团队在学术期刊Applied Physics Letters发布了一篇名为214 MW/cm2 vertical β-Ga2O3 UMOSFETs enabled by HF sidewall treatment(通过 HF 侧壁处理实现 214 MW/cm2 垂直 β-Ga2O3 UMOSFET)的文章。

背 景

β-Ga2O3 作为下一代超宽禁带半导体材料,因其约 4.8 eV 的宽禁带、高临界电场以及优异的 Baliga 指数,成为高功率、低损耗电子器件的理想候选,同时可通过成本较低的熔体生长法制备大面积、高质量单晶衬底,为器件应用提供坚实材料基础。然而,β-Ga2O3 缺乏可靠的 p 型掺杂,使传统 pn 结器件难以实现,限制了高性能垂直晶体管的发展。为此,研究者提出了带电流阻挡层(CBL)的垂直 MOSFET 和鳍状场效应晶体管(FinFET)等替代结构,通过调控载流子实现增强型工作模式,其中 U 型沟槽结构(UMOSFET)因单元密度高、输入电容低而受到关注。提升 CBL 的击穿能力是关键,但深受载流子补偿效应影响,通常存在击穿电压与沟道电阻的权衡。近年来的研究表明,氟掺杂或 HF 处理可修复氧空位并引入浅能级杂质,从而增强 n 型导电性,改善器件开态性能,并提供了一种低成本、简便的优化路径。因此,本研究基于 HF 湿化学处理对 β-Ga2O3 UMOSFET 沟槽侧壁进行选择性氟掺杂,以提升沟道导电性能、保持 CBL 电流阻挡能力,并缓解击穿电压与漏电流之间的权衡问题。

主要内容

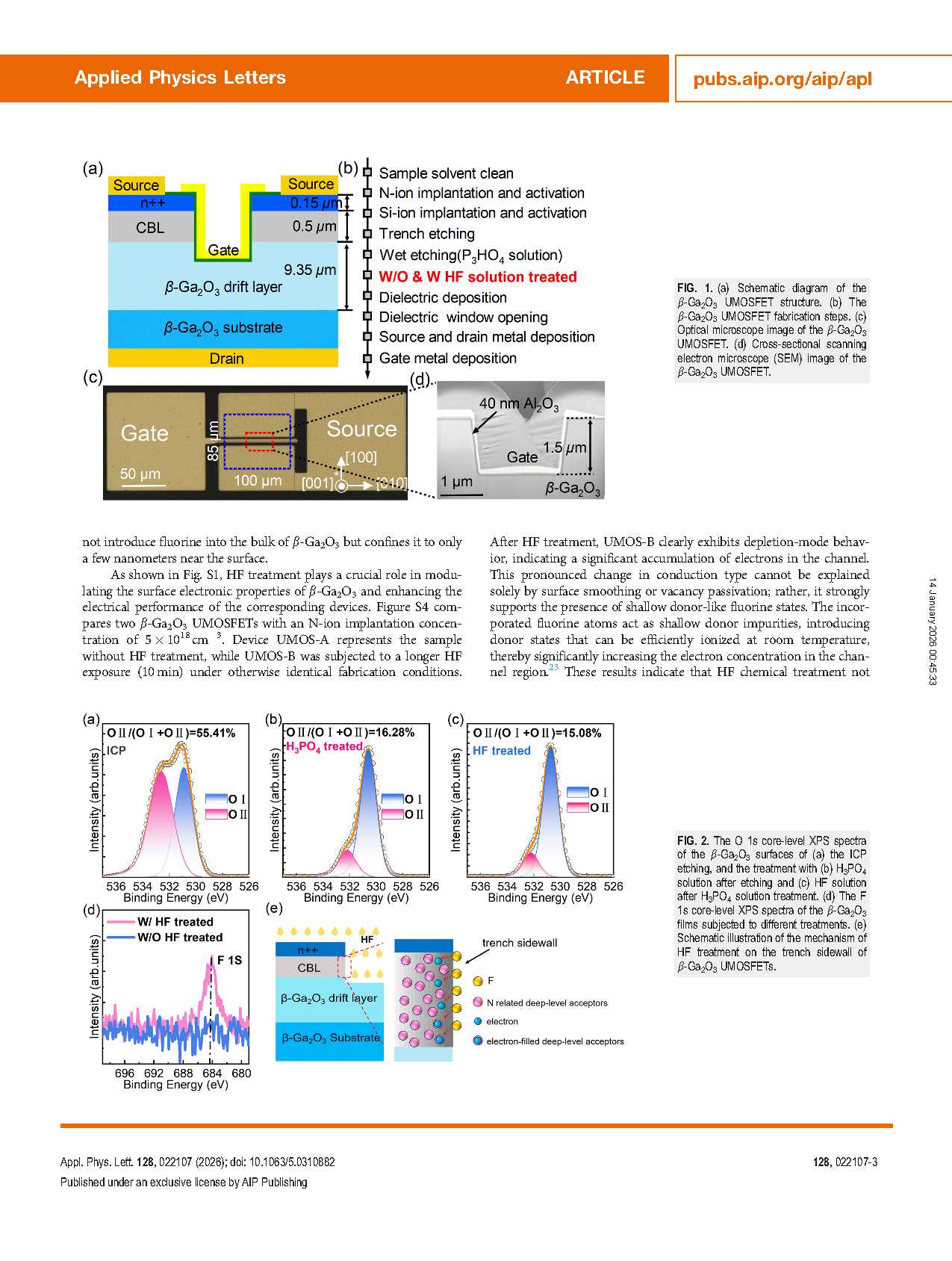

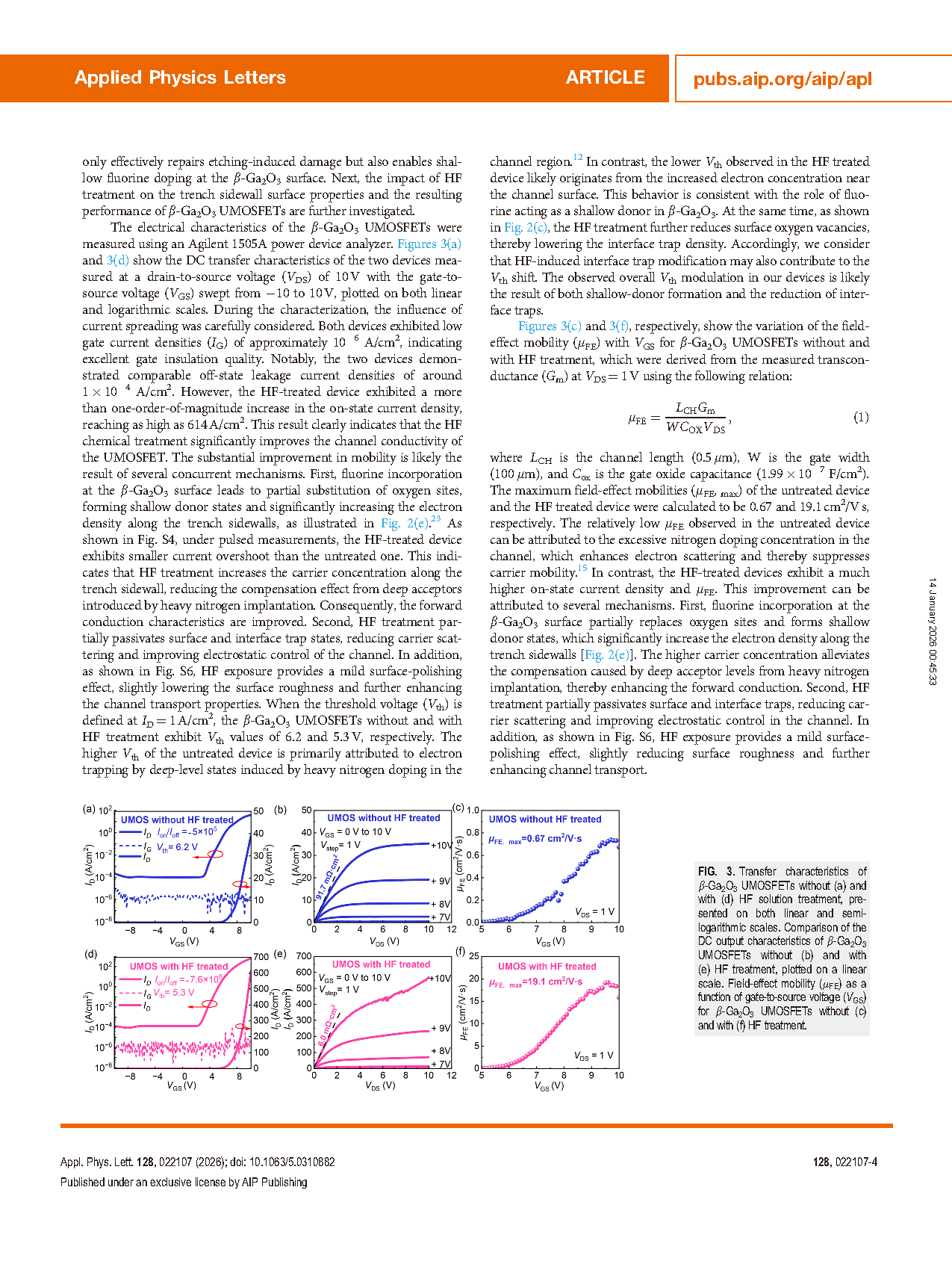

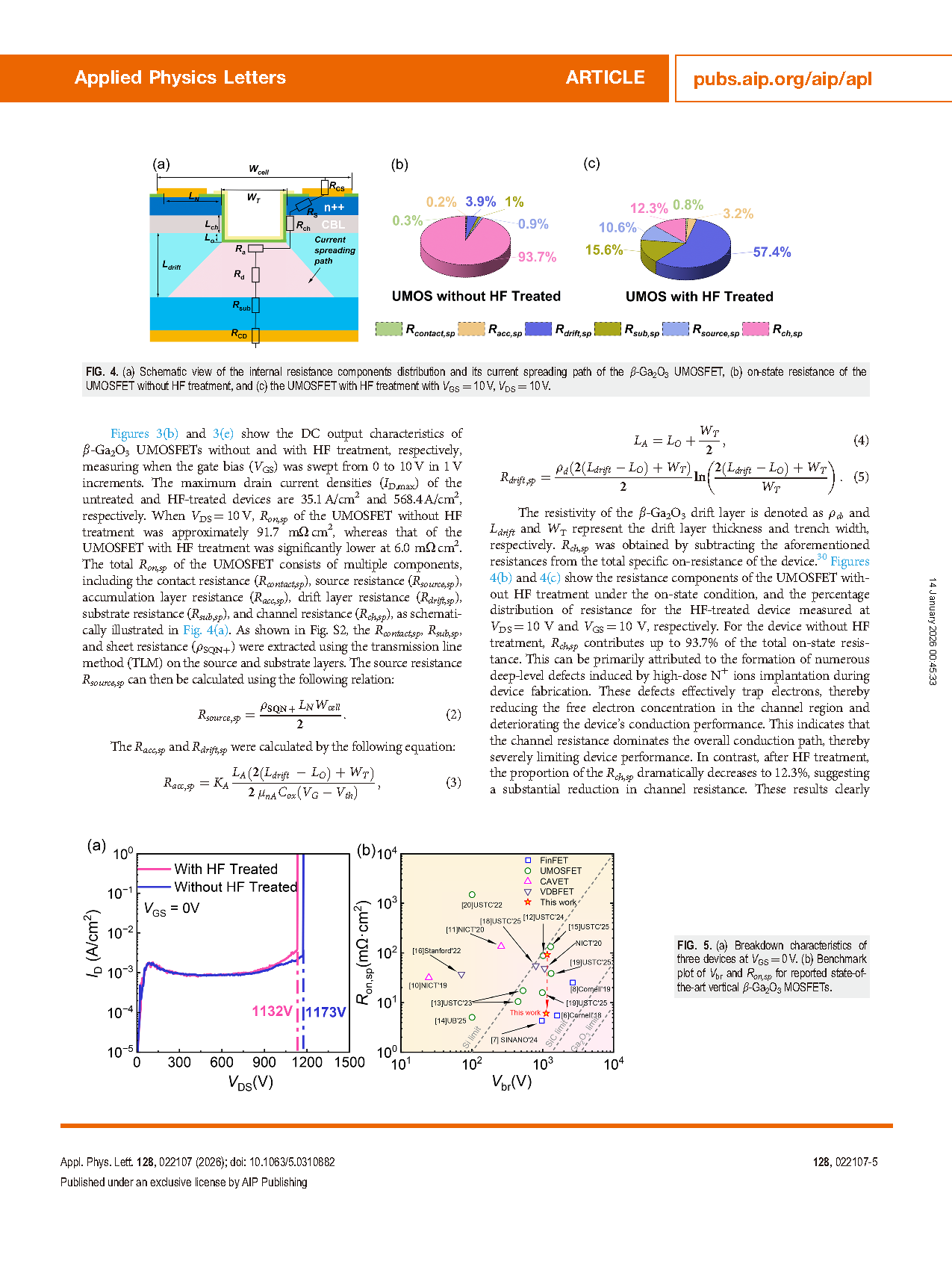

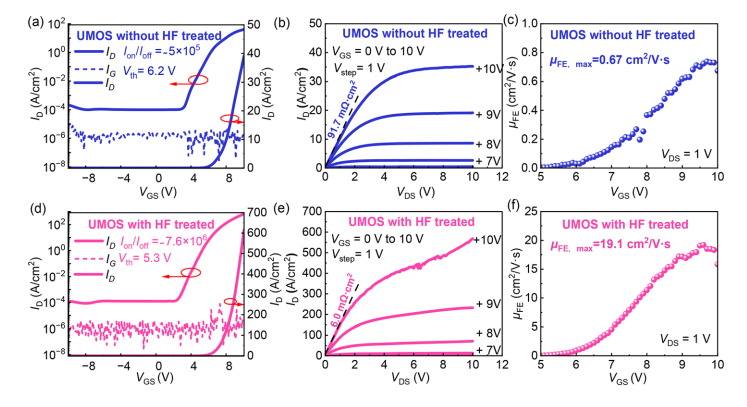

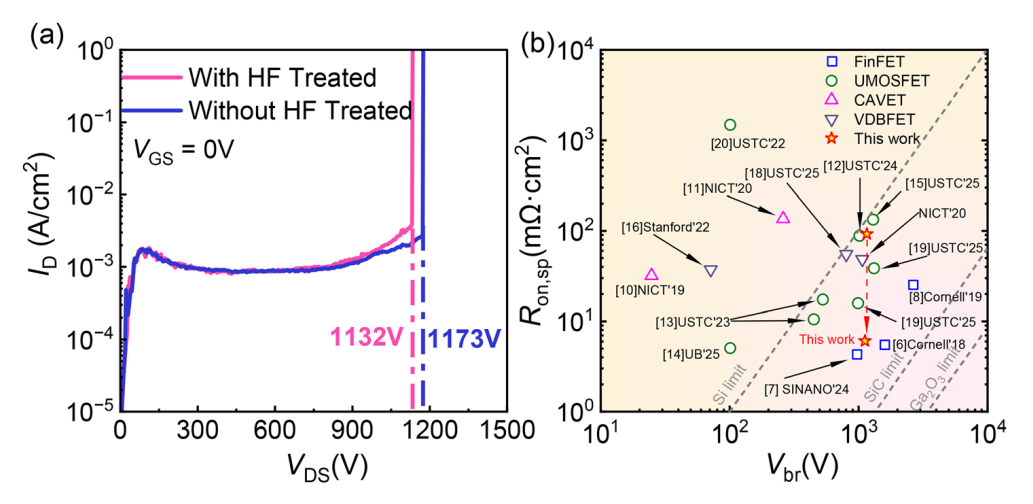

垂直 β-Ga2O3 U 形沟槽结构(UMOSFET)中嵌入电流阻挡层(CBL)通常存在导通电阻增加的问题,这主要是由于沟槽侧壁的深能级缺陷态俘获自由电子所致。在本研究中,在栅极介电层沉积前引入了氢氟酸(HF)侧壁处理,以修饰沟槽表面。该工艺能够将氟原子有效引入侧壁区域,提高电子浓度,并缓解由重氮掺杂引入的深受主能级的补偿效应,从而改善正向导通性能。此外,HF 处理还能部分钝化表面和界面陷阱,并具有轻微的抛光作用,从而略微降低表面粗糙度。这些改变有助于抑制界面散射,进一步增强载流子输运。制备的垂直 β-Ga2O3 UMOSFETs 实现了 6.0 mΩ·cm2 的比导通电阻、19.1 cm2/V·s 的沟道迁移率以及 1132 V 的击穿电压。这些结果表明,HF 侧壁处理为显著提升 β-Ga2O3 UMOSFETs 导电性能和整体电学特性提供了一种简单高效的表面工程方法。

创新点

● HF 侧壁处理:首次对 β-Ga2O3 UMOSFET 沟槽侧壁进行 HF 湿法刻蚀,有效减轻刻蚀损伤。

● 氟原子掺入:HF 处理引入氟作为浅施主,提高沟道载流子浓度。

● 导通性能提升:比导通电阻大幅降低,沟道迁移率显著提升,同时保持反向阻断能力。

● 界面优化:部分钝化表面/界面陷阱并轻微抛光,改善载流子传输。

● 低成本可行策略:提供简单高效的表面工程方法,利于高性能器件开发。

结 论

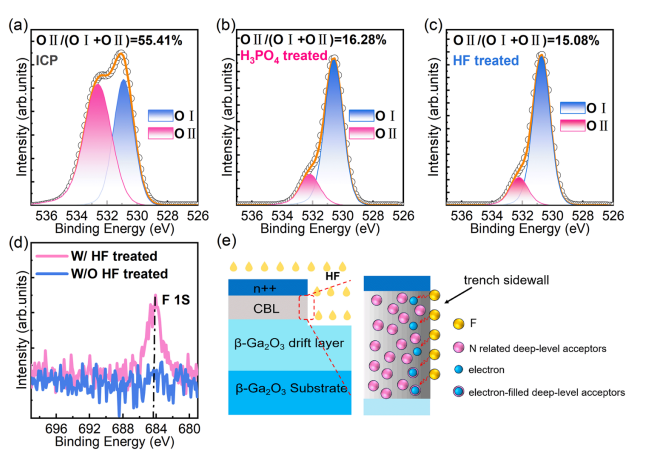

本研究通过对沟槽侧壁进行 HF 处理,成功制备出高性能 β-Ga2O3 UMOSFET。XPS 分析表明,HF 处理能够有效缓解等离子体刻蚀引起的损伤,并在 β-Ga2O3 表面引入氟掺杂。掺入的氟原子作为浅施主形成高导电性的沟道,提高了载流子浓度,从而显著提升器件的导电性能。与未进行 HF 处理的器件相比,比导通电阻 Ron,sp 从 91.7 mΩ·cm2 显著降低至 6.0 mΩ·cm2,而最大沟道迁移率 uFE,max 从 0.67 cm2/V·s 提升至 19.1 cm2/V·s,同时反向阻断能力未受到任何影响。这项工作为开发高性能、低成本的 β-Ga2O3 功率器件提供了一条有前景的策略。

项目支持

本工作部分得到以下项目资助:江苏省基础研究计划(项目编号:BK20253003)、苏州市关键核心技术研究项目(项目编号:SYG2024003)、国家重点基础研究发展计划(项目编号:2021YFC2203400)以及江西省重点研发计划(项目编号:20223BBE51033)。作者感谢中国科学院苏州纳米技术与纳米仿生研究所的纳米制造设施及真空互联纳米技术工作站(NANO-X)提供的技术支持。

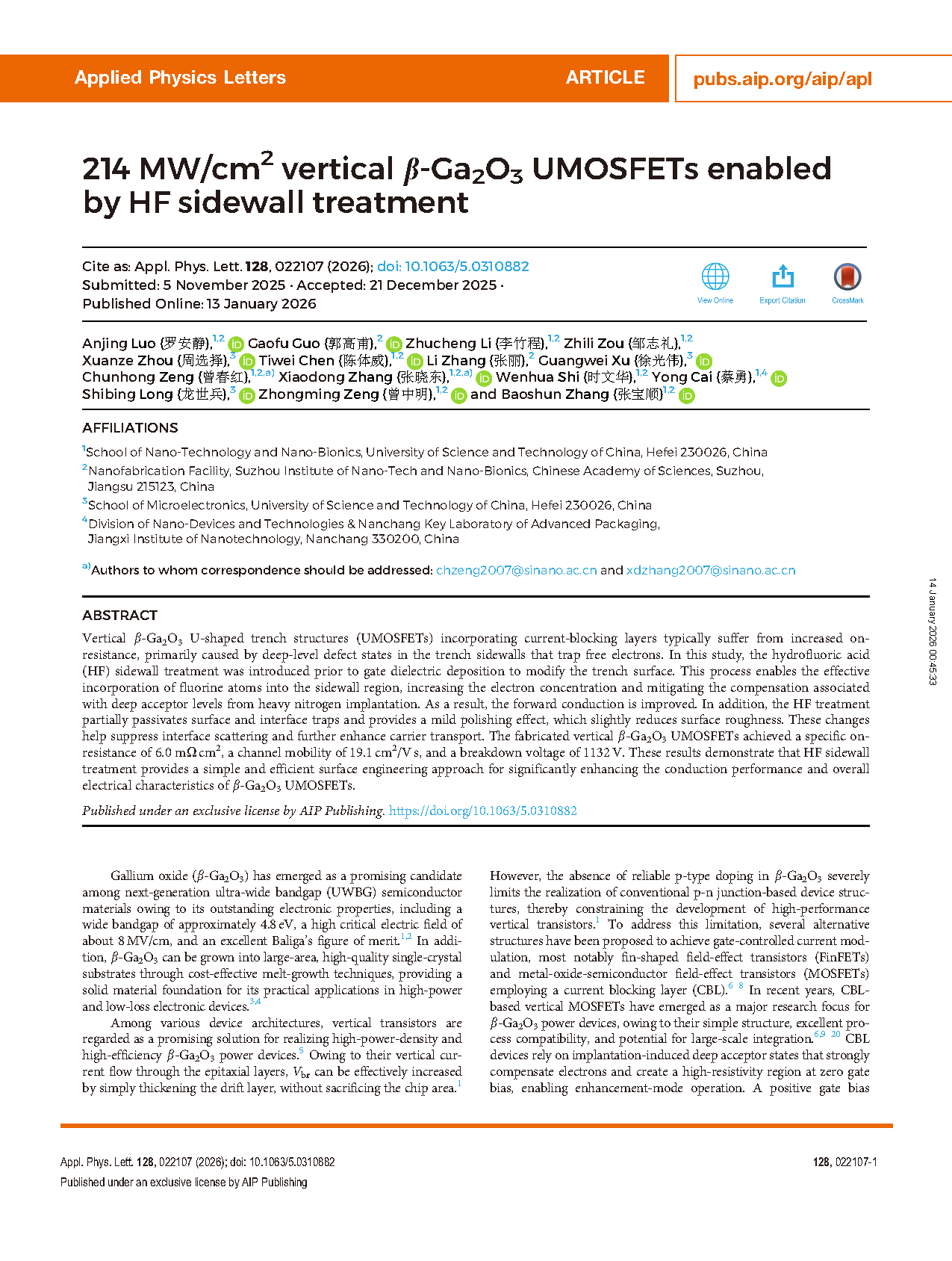

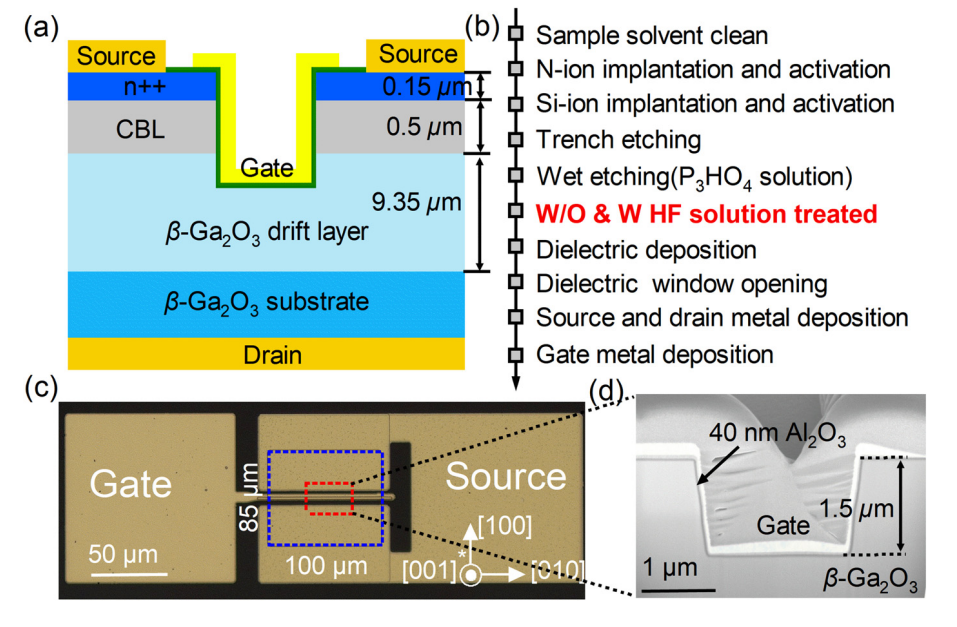

FIG. 1.(a) β-Ga2O3 UMOSFET 结构示意图。(b) β-Ga2O3 UMOSFET 的器件制备流程。(c) β-Ga2O3 UMOSFET 的光学显微镜图像。(d) β-Ga2O3 UMOSFET 的截面扫描电子显微镜(SEM)图像。

FIG. 2. (a) ICP 刻蚀后 β-Ga2O3 表面的 O 1s 核能级 XPS 谱;(b) 刻蚀后经 H3PO4 溶液处理的 β-Ga2O3 表面 O 1s 核能级 XPS 谱;(c) 在 H3PO4 处理基础上进一步经 HF 溶液处理后的 β-Ga2O3 表面 O 1s 核能级 XPS 谱;(d) 不同处理条件下 β-Ga2O3 薄膜的 F 1s 核能级 XPS 谱;(e) HF 处理对 β-Ga2O3 UMOSFET 沟槽侧壁作用机制的示意图。

FIG. 3. (a)、(d) 分别为未进行 HF 溶液处理和经过 HF 溶液处理的 β-Ga2O3 UMOSFET 的转移特性曲线,采用线性坐标和半对数坐标表示;(b)、(e) 分别为未进行 HF 处理和经过 HF 处理的 β-Ga2O3 UMOSFET 的直流输出特性对比(线性坐标);(c)、(f) 分别为未进行 HF 处理和经过 HF 处理的 β-Ga2O3 UMOSFET 的场效应迁移率(μFE)随栅源电压(VGS)变化的关系。

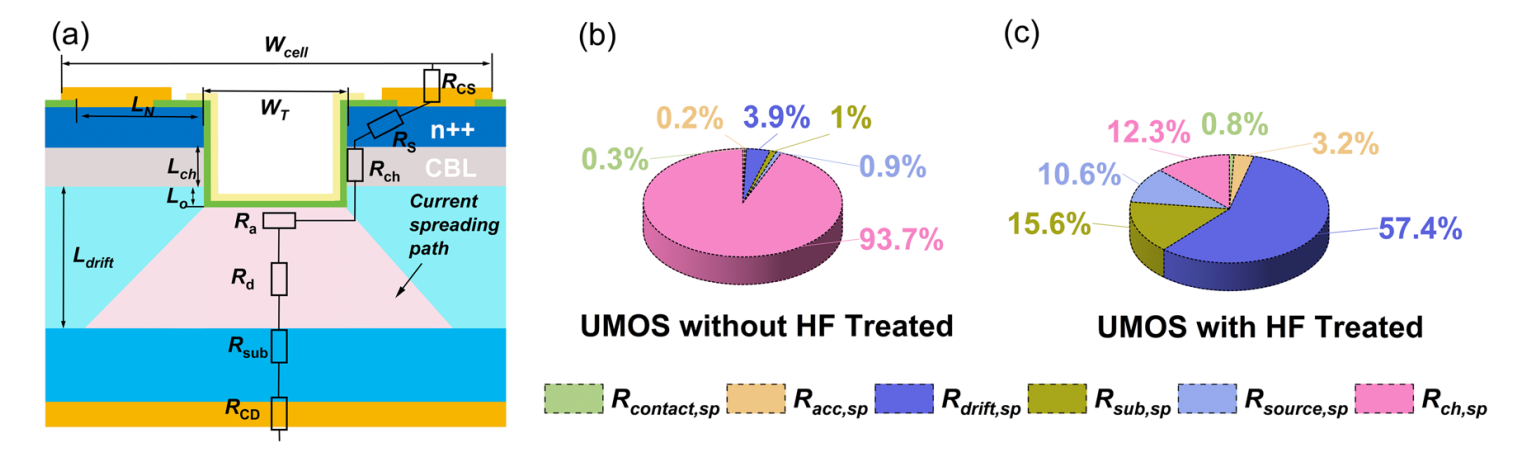

FIG. 4.(a) β-Ga2O3 UMOSFET 内部电阻组成及电流扩展路径的示意图;(b) 未经 HF 处理的 UMOSFET 的导通电阻分布;(c) 经 HF 处理的 UMOSFET 在 VGS = 10 V、VDS = 10 V 条件下的导通电阻分布。

FIG. 5. (a) 在 VGS = 0 V 条件下三种器件的击穿特性; (b) 已报道的先进垂直 β-Ga2O3 MOSFET 的击穿电压(Vbr)与比导通电阻(Ron,sp)基准对比图。

DOI:

doi.org/10.1063/5.0310882