【国际论文】ACS AEM丨英国布里斯托大学:采用H₃PO₄处理抑制 2.7 kV β-Ga₂O₃(001)沟槽肖特基势垒二极管中等离子体刻蚀诱导的负电荷捕获效应

日期:2026-03-17阅读:148

由英国布里斯托大学的研究团队在学术期刊 ACS Applied Electronic Materials 发布了一篇名为 Mitigating Plasma Etch-Induced Negative Charge Trapping in 2.7 kV β-Ga2O3 (001) Trench Schottky Barrier Diodes Using H3PO4 Treatment (采用 H3PO4 处理抑制 2.7 kV β-Ga2O3 (001) 沟槽肖特基势垒二极管中等离子体刻蚀诱导的负电荷捕获效应)的文章。

背 景

随着功率电子器件向高压、高效率方向发展,超宽带隙半导体 β-Ga2O3 因其卓越的临界击穿电场(8 MV cm-1)而备受关注。为了提升其击穿电压,研究者通常采用沟槽肖特基势垒二极管(TSBD)结构来优化电场分布,但在制造过程中,干法电感耦合等离子体(ICP)刻蚀不可避免地会在侧壁引入缺陷和负电荷陷阱。这些缺陷会导致器件在反向偏压应力下出现开启电压偏移和导通电阻(Ron)退化,严重影响器件的稳定性和可靠性。因此,寻找一种有效的表面处理方法来修复刻蚀损伤,成为实现高性能氧化镓功率器件的关键。

主要内容

通过在器件制造过程中采用磷酸表面处理来降低 Al2O3/Ga2O3 界面态陷阱密度,成功展示了具有巴利加优值(BFOM)为 0.7 GW cm–2 的稳定 β-Ga2O3(001)沟槽肖特基势垒二极管(TSBD)。对沿不同方向的 fins 的 TSBD 进行了研究,其中采用 H3PO4 处理的 [010] fin 结构器件表现出 11 mΩ cm2 的低比导通电阻(Ron,sp)和高达 2.7 kV 的击穿电压。通过在反向偏压高达 -1.2 kV 下进行的连续电压应力可靠性测试表明,未经处理的器件的 Ron,sp 降低了 20%,而采用 H3PO4 表面处理的器件仅降低了 9%。TCAD 模拟证实,H3PO4 处理减轻了负界面电荷的密度,突显了酸处理在控制缺陷介导的不稳定性方面的有效性。此外,高温偏置应力测试表明,经过处理的 [010] 方向的 TSBD 实现了卓越的热稳定性和电稳定性,消除了未经处理器件中观察到的 10% 的 Ron,sp 增加。这些结果表明,H3PO4 表面处理是增强 β-Ga2O3 功率器件在热电联合应力下稳健性的有效策略。

创新点

● 通过采用 H3PO4(磷酸)化学处理,研究成功研制出击穿电压(Vbr)高达 2.7 kV 的(001) β-Ga2O3 沟槽二极管。其功率优值(BFOM)达到 0.7 GW/cm2 ,相比未经处理的器件提升了约 45%。

● 在 -1.2 kV 的高额定电压应力测试下,经过处理的器件导通电阻退化率从原来的 20% 显著降低至 9%。更重要的是,处理后的器件在应力移除后表现出更快的恢复速度,证明了 H3PO4 能有效减少不稳定的电荷捕获效应。

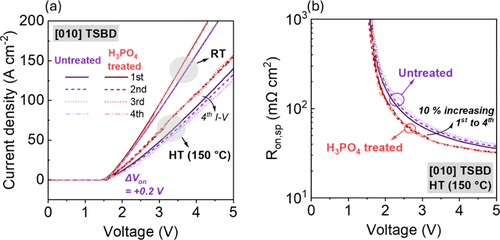

● 研究展示了器件在 150°C 高温下的稳定性。未处理器件在高温循环测量中会出现约 10% 的导通电阻增加,而经过磷酸处理的器件则表现出极高的重复性,消除了由于刻蚀诱导缺陷引起的热不稳定现象。

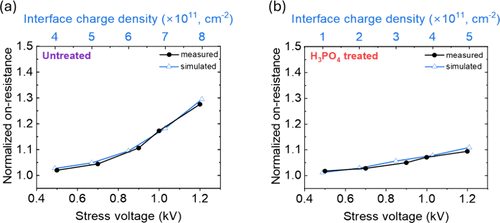

● 结合 TCAD 仿真分析,研究证实了 H3PO4 处理能将沟槽底部的负界面电荷密度从 3×1011cm-2 降低到 9×1010cm-2 以下。此外,研究还发现沿着 [010] 晶向的沟槽侧壁具有最佳的初始性能和抗退化能力。

结 论

研究团队通过测量和模拟研究了 H3PO4 表面处理对 β-Ga2O3 TSBD 在高温和偏置应力下的电性能和可靠性的影响。在室温下,该处理确保了 [140] 和 [120] 取向的 TSBD 稳定运行,而 [010] 取向的 TSBD 则实现了显著的性能提升,Ron,sp 从 13 降至 11 mΩ cm2,Vbr 从 2.5 升至 2.7 kV,从而 BFOM 达到约 0.7 GW cm-2 。在高达 -1.2 kV 的反向偏置下进行连续电压应力测试时,未经处理的器件 Ron,sp 增加了 26%,而 H3PO4 处理过的器件仅增加了 11%,且仅需 1 小时即可基本恢复。此外,在 150°C 的高温可靠性测试中,H3PO4 处理过的 TSBD 在多次测量中保持了稳定的性能,而未经处理的器件 Ron,sp 增加了 10%,Von 发生了正向偏移。总体而言,这些发现强调了在器件加工过程中通过表面处理来控制界面电荷和表面缺陷的重要性,这对于实现 β-Ga2O3 阻塞二极管在电热联合应力下的稳健可靠运行至关重要,为在恶劣环境中实现高压电力电子器件铺平了道路。

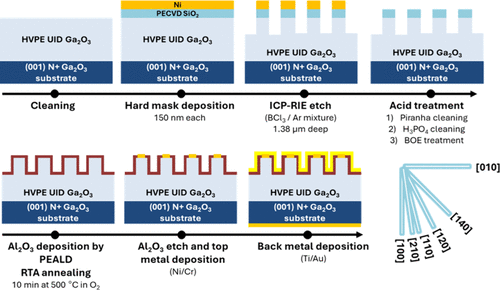

图 1. 本研究中所实现的不同 fin 取向的 TSBD 的结构示意图及其制造工艺流程。

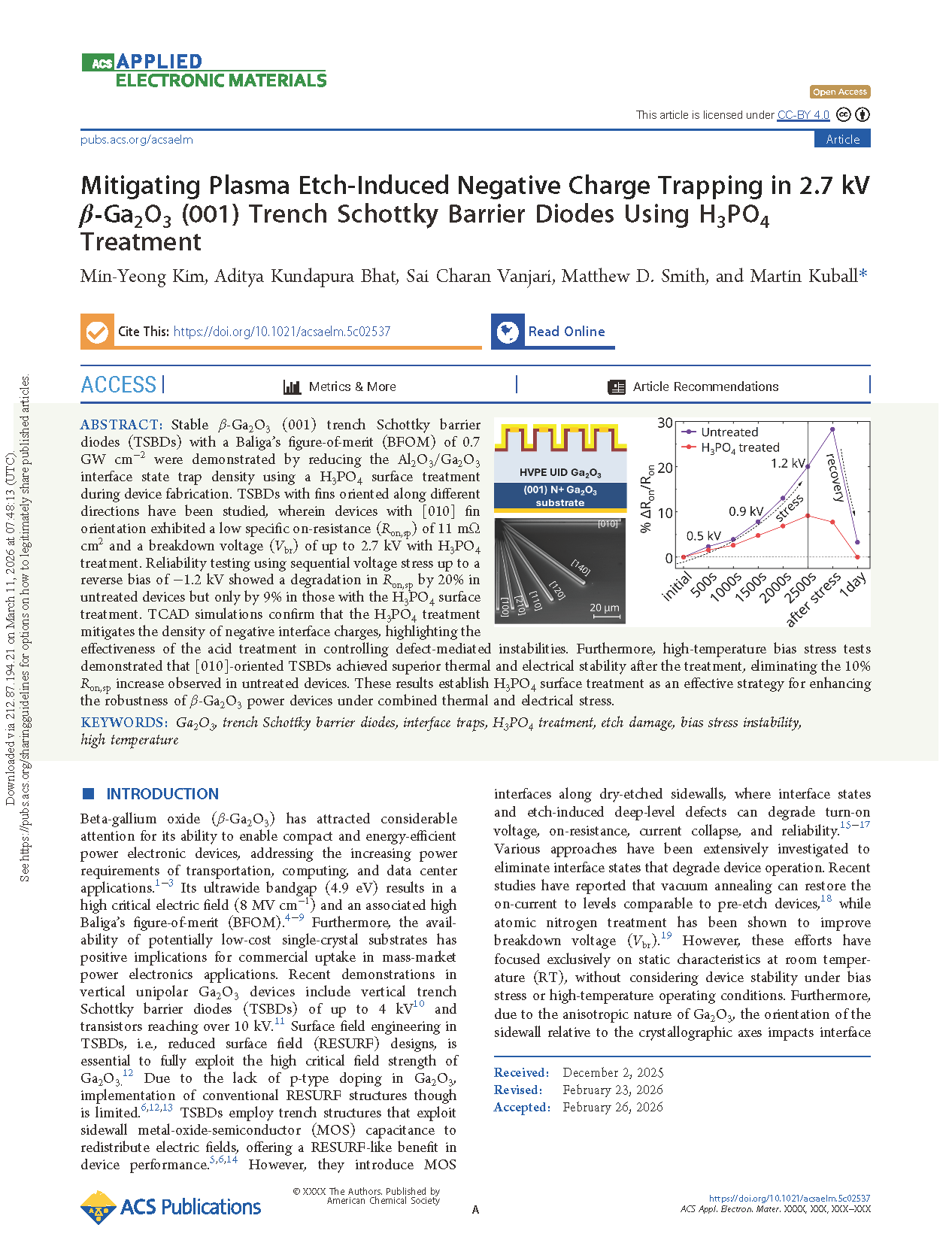

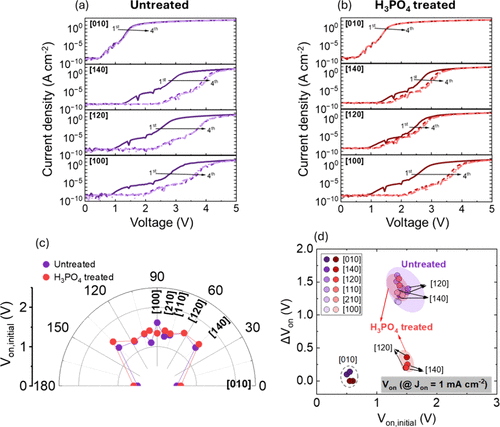

图2: 不同 fin 取向的 Ga2O3 TSBD 在0至5 V 范围内的重复电流密度-电压(J-V)特性:(a) 未处理和(b)H3PO4 处理的 TSBD;(c)未处理和 H3PO4 处理下,Von,initial 随 fin 取向的变化;(d)在室温下,从 0 至5 V 重复电压扫描时测得的 ΔVon 与 Von,initial 的汇总图。ΔVon 表示第四次测量与初始测量之间 Von 的偏移。

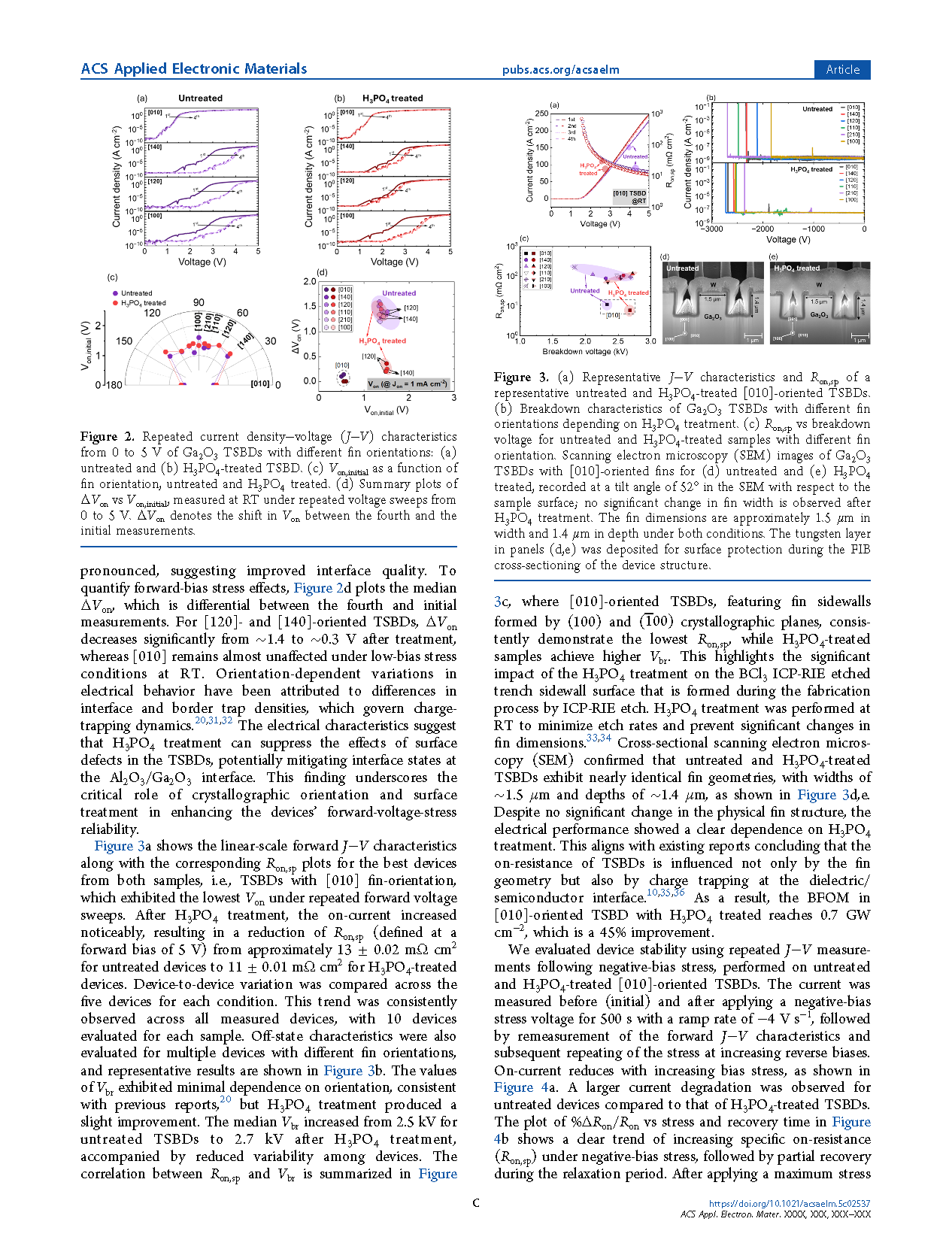

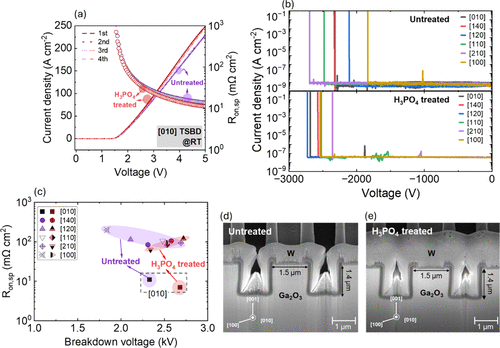

图3. (a) 代表性未处理和 H3PO4 处理的 [010] 取向 TSBDs 的代表性 J–V 特性和 Ron,sp;(b) 不同fin 取向的 Ga2O3 TSBDs 在 H3PO4 处理后的击穿特性;(c) 不同 fin 取向的未处理和 H3PO4 处理样品的 Ron,sp 与击穿电压的关系;图(d)和(e)分别为未处理和 H3PO4 处理的 [010] 取向 fin 的 Ga2O3 TSBDs 的扫描电子显微镜(SEM)图像,在 SEM 中相对于样品表面倾斜 52° 角记录;H3PO4 处理后,fin 宽度未观察到显著变化。在两种条件下,fin 的尺寸约为 1.5 μm 宽、1.4 μm 深。图(d,e)中的钨层是在对器件结构进行聚焦离子束(FIB)横截面切割时沉积的,用于表面保护。

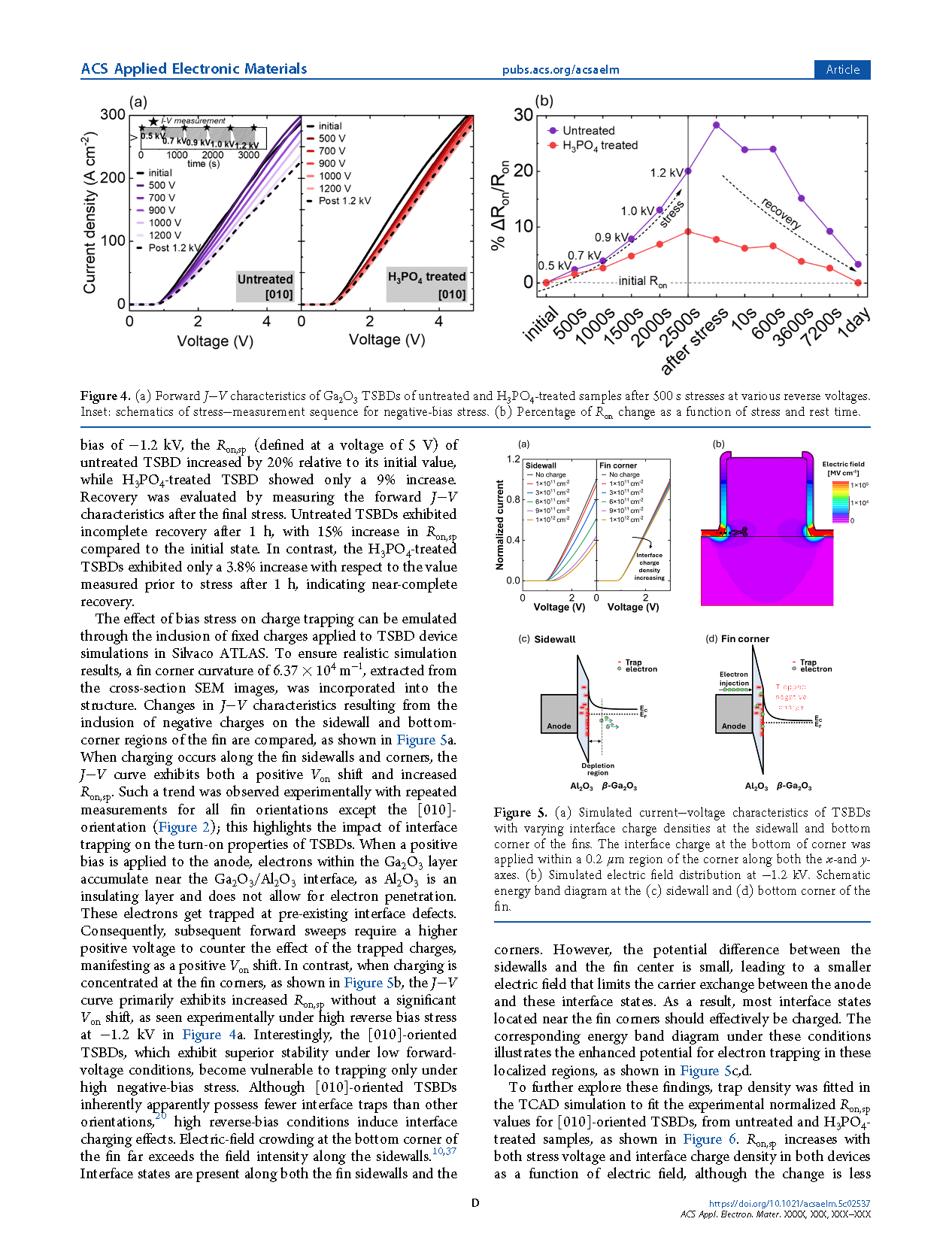

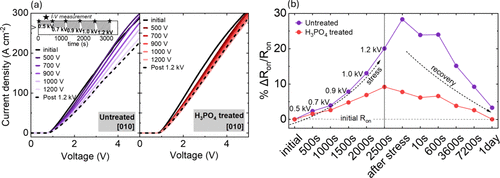

图4. (a) 在不同反向电压下施加 500 秒应力后,未处理和 H3PO4 处理样品的 Ga2O3 TSBD的正向 J-V 特性。插图:负偏压应力下应力测量顺序示意图;(b) Ron 变化百分比与应力和休息时间的关系。

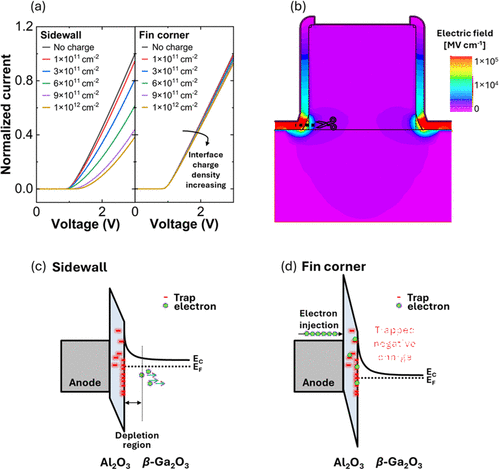

图5. (a)模拟了 fin 侧壁和底角处界面电荷密度变化时 TSBDs 的电流-电压特性。底角处的界面电荷是在沿 x 轴和 y 轴的 0.2 μm 区域内施加的;(b)模拟 -1.2 kV 下的电场分布。能带示意图;(c)侧壁;(d)fin 的底角的能带示意图。

图6. 模拟的归一化 Ron,sp 与测量结果的对比,作为器件应力电压的函数,其中(a)为未处理器件,(b)为通过调整 fin 角落的界面电荷密度以符合实验数据的 H3PO4 处理器件。

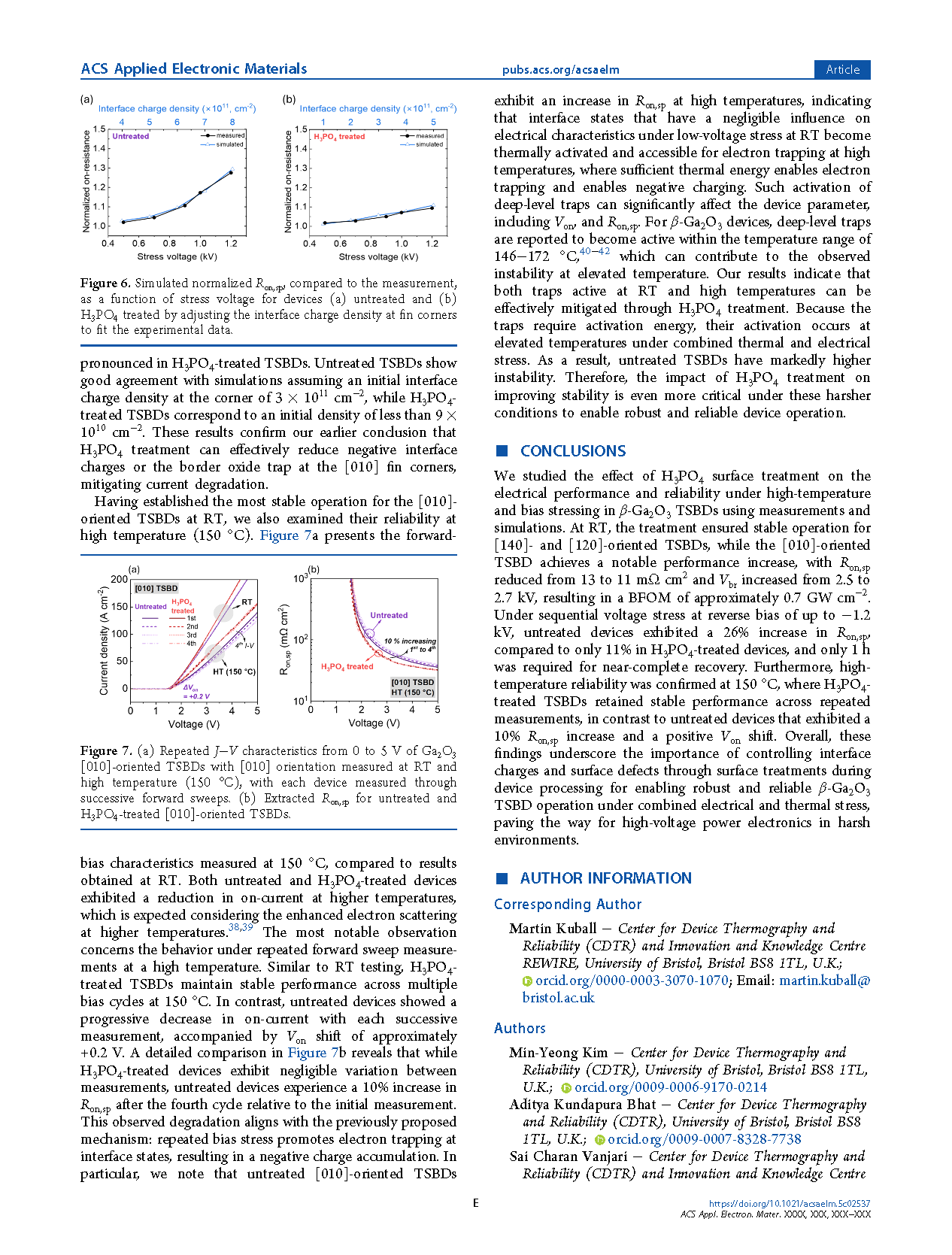

图7. (a) 在室温(RT)和高温(150°C)下测量的具有 [010] 取向的Ga2O3[010] 取向 TSBDs在 0 至 5 V 范围内的重复 J-V 特性,每个器件均通过连续的正向扫描进行测量; (b) 提取的未处理和 H3PO4 处理的 [010] 取向 TSBDs 的 Ron,sp。

DOI:

doi.org/10.1021/acsaelm.5c02537