【国际论文】日本京都工艺纤维大学、高知工业大学、金泽工业大学、明治大学:具有 GZO 缓冲层的 Si (100) 衬底上多晶κ-Ga₂O₃薄膜

日期:2026-04-15阅读:49

由日本京都工艺纤维大学、高知工业大学、金泽工业大学、明治大学的研究团队在学术期刊RSC Advances发布了一篇名为Polycrystalline κ-Ga₂O₃ on Si(100) substrates with GZO buffer layers(具有 GZO 缓冲层的 Si (100) 衬底上多晶 κ-Ga₂O₃ 薄膜)的文章。

背 景

κ-Ga₂O₃ 是一种新型压电半导体,在射频器件中具有应用潜力,但硅衬底上异质外延生长因晶格失配与界面氧化问题难度较大。传统外延方法依赖 AlN、Mo 等单晶缓冲层,而面向实用化的压电器件,晶体各向同性对设计灵活性至关重要。本研究首次采用 GZO 缓冲层,在 Si (100) 上实现多晶 κ-Ga₂O₃ 生长,工艺更简单且薄膜具备各向同性,更适合硅基集成。

主要内容

κ 相氧化镓(κ-Ga₂O₃)是一种新兴的压电半导体,在射频器件中具有潜在应用。然而,由于晶格失配度大及界面氧化,在硅衬底上异质外延生长 κ-Ga₂O₃ 仍面临挑战。本研究采用雾化化学气相沉积(mist CVD)技术,在 Si (100) 衬底上利用掺镓氧化锌(GZO)缓冲层制备了多晶 κ-Ga₂O₃ 薄膜。通过 X 射线衍射、扫描电子显微镜和透射电子显微镜进行结构表征,结果表明 κ-Ga₂O₃ 薄膜呈现 c 轴取向、面内随机分布的多晶结构,具备对器件应用有利的各向同性特性。在 κ-Ga₂O₃/GZO 界面处发现了 ZnGa₂O₄ 中间层,该层对相稳定起关键作用。研究结果表明,硅衬底上的多晶 κ-Ga₂O₃ 是压电半导体器件的理想候选体系。

创新点

●首次在 Si (100) 衬底上采用 GZO 多晶缓冲层制备纯相多晶 κ-Ga₂O₃ 薄膜,替代传统 AlN/Mo 单晶缓冲方案。

●薄膜呈 c 轴择优取向、面内晶粒随机分布,实现优异各向同性,更利于压电器件设计。

●界面原位形成 ZnGa₂O₄ 中间层,有效稳定 κ 相,抑制杂相生成。

●采用 mist CVD 常压低温工艺,成本低、与硅基 CMOS 兼容潜力高。

总 结

本研究成功采用雾化化学气相沉积(mist CVD)技术,在 Si (100) 衬底上利用 GZO 缓冲层制备了多晶 κ-Ga₂O₃ 薄膜。c 轴取向的 GZO 缓冲层因具有六方氧原子排列结构,可促进 κ Ga₂O₃ 的形成。硅衬底表面的非晶 SiO₂阻碍了 κ-Ga₂O₃/GZO/Si 体系中外延关系的建立,使 κ Ga₂O₃ 呈多晶生长。与采用 AlN、Mo 等外延缓冲层的以往研究不同,多晶 GZO 缓冲层工艺更简单,且薄膜天然具备各向同性,更适合将基于 κ-Ga₂O₃ 的压电器件与硅技术集成。结构分析表明,κ-Ga₂O₃ 薄膜呈随机晶体取向,固有各向同性对压电器件应用有利。界面处 ZnGa₂O₄ 中间层的形成是稳定 κ 相的关键因素。与具有规则旋转畴的传统外延 κ-Ga₂O₃ 薄膜不同,本研究的多晶薄膜各向同性更完备,且在重要的硅衬底上生长工艺更简化。该结果为基于 κ-Ga₂O₃ 的压电器件与硅技术集成开辟了新路径。通过进一步优化生长条件与缓冲层设计,有望实现多晶 κ-Ga₂O₃ 薄膜的高性能压电应用。

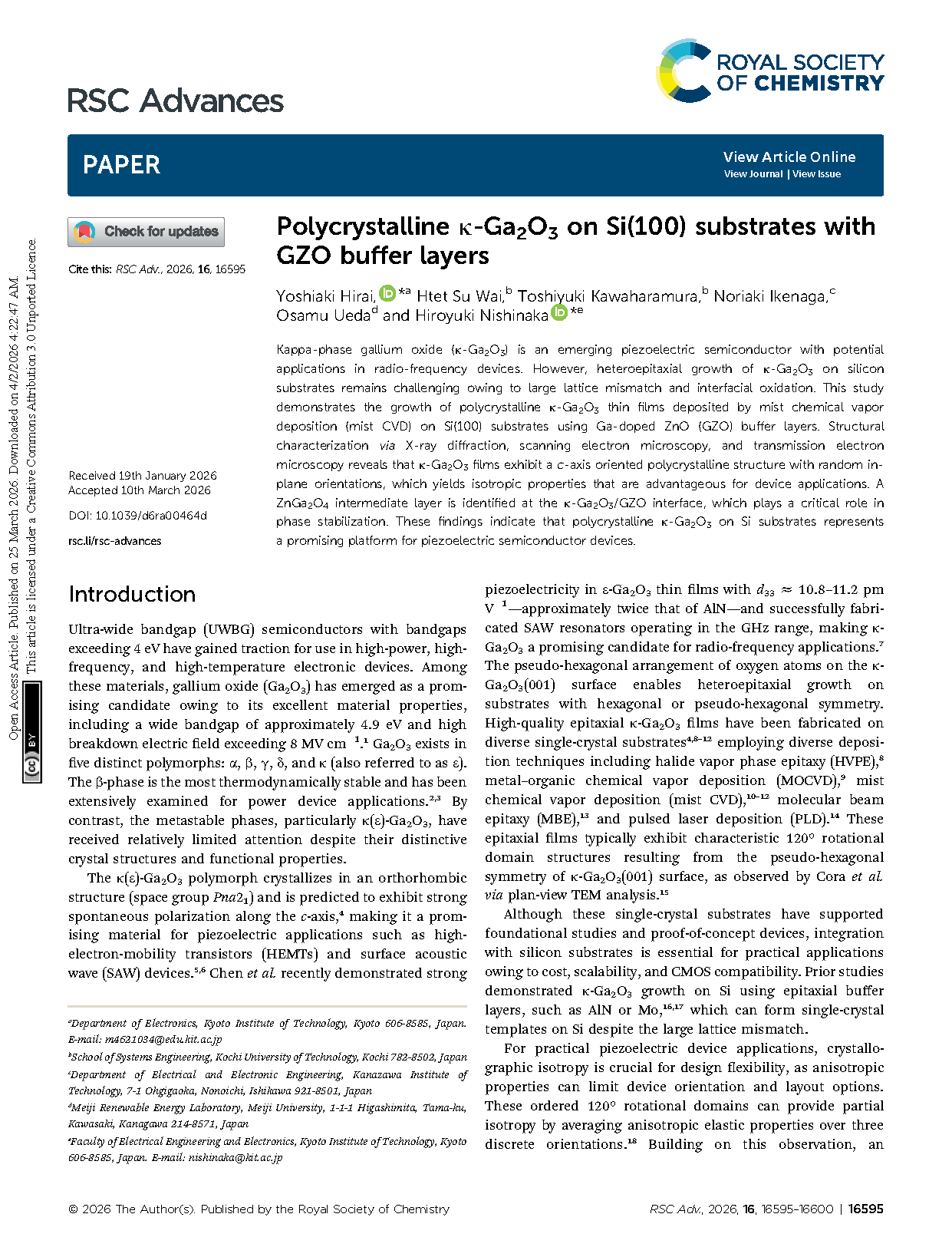

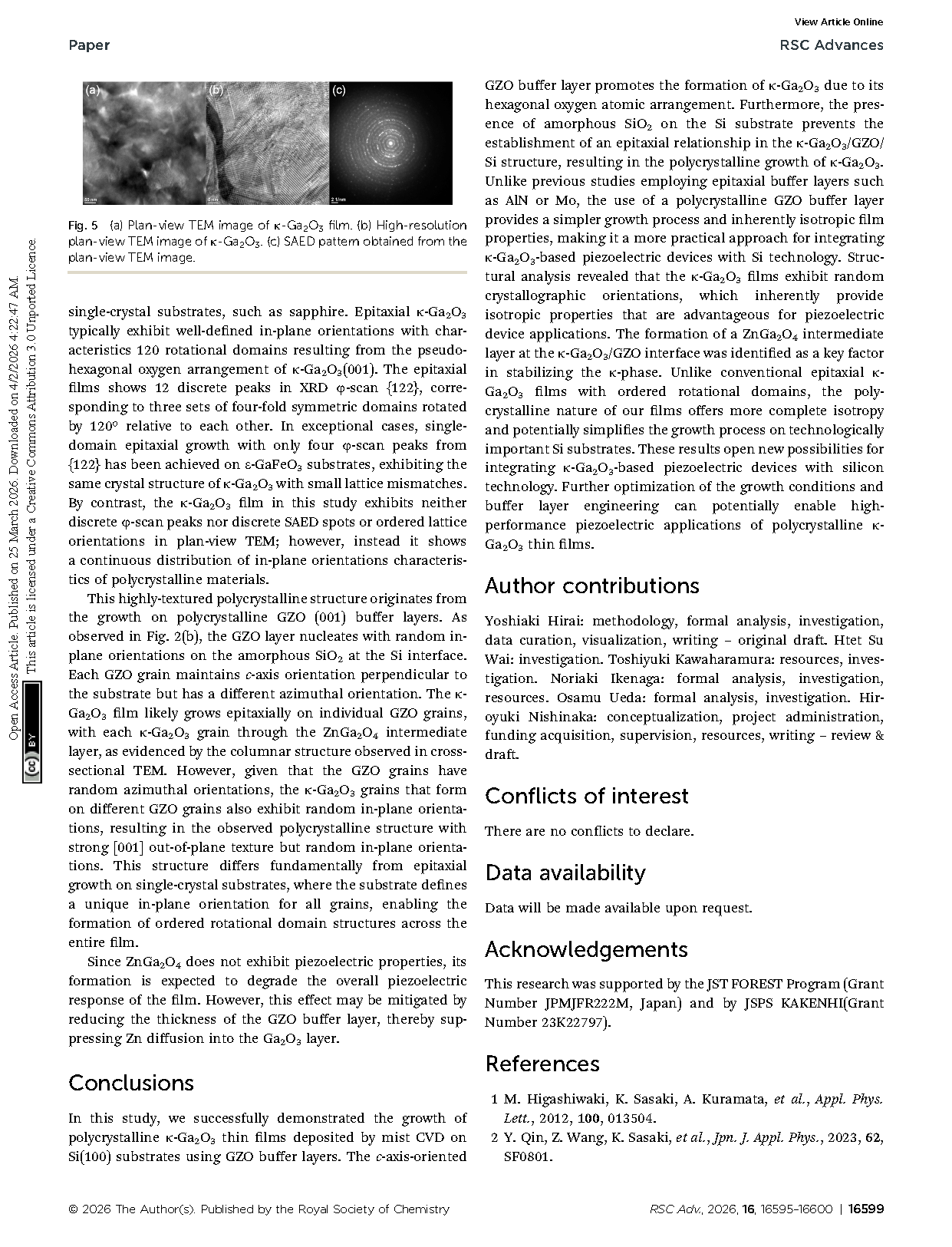

图 1 (a) 在 GZO/Si 上生长的 κ‑Ga₂O₃ 的 XRD 2θ–ω 扫描图谱;(b) 三层结构的 XRD φ‑scan 扫描图谱。

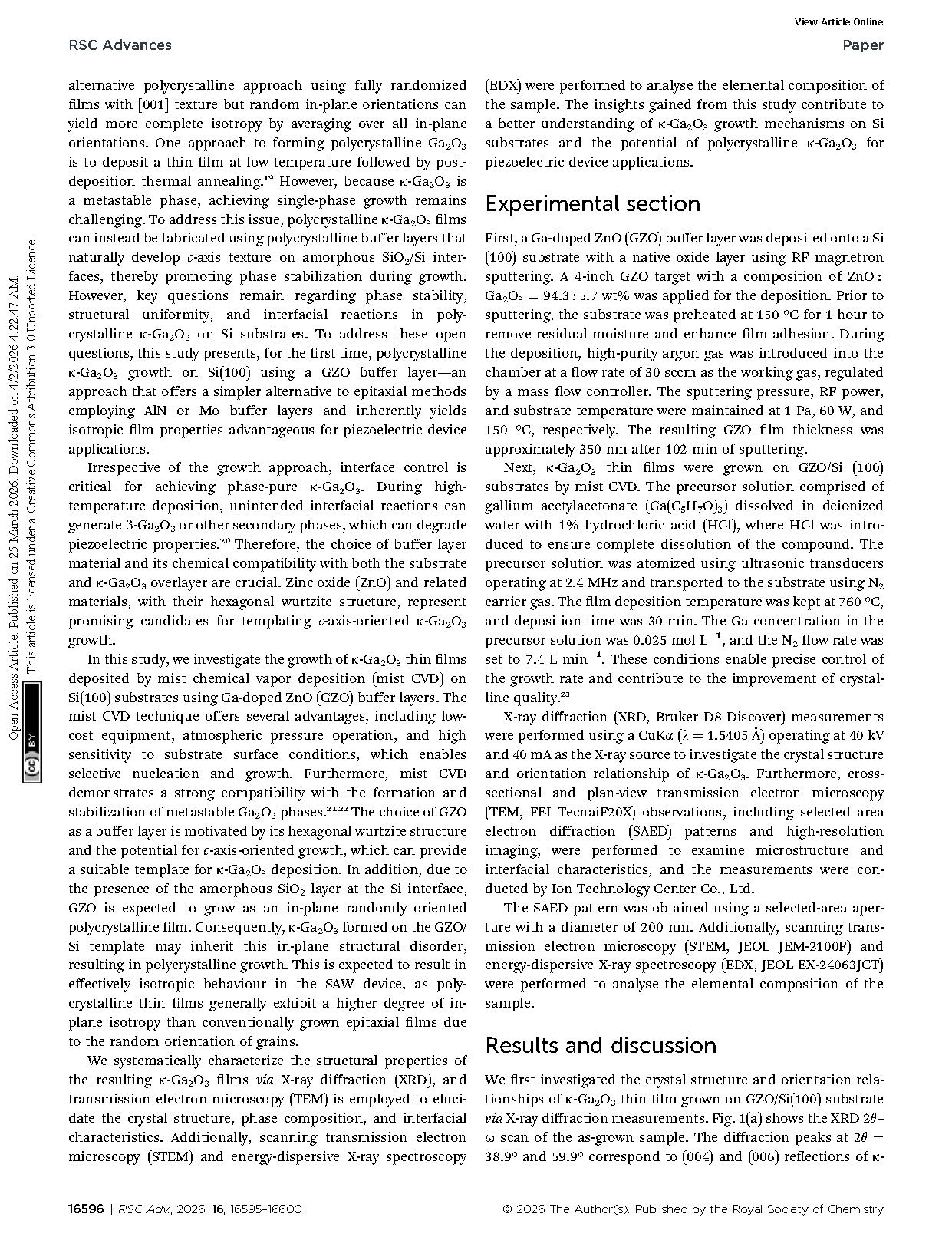

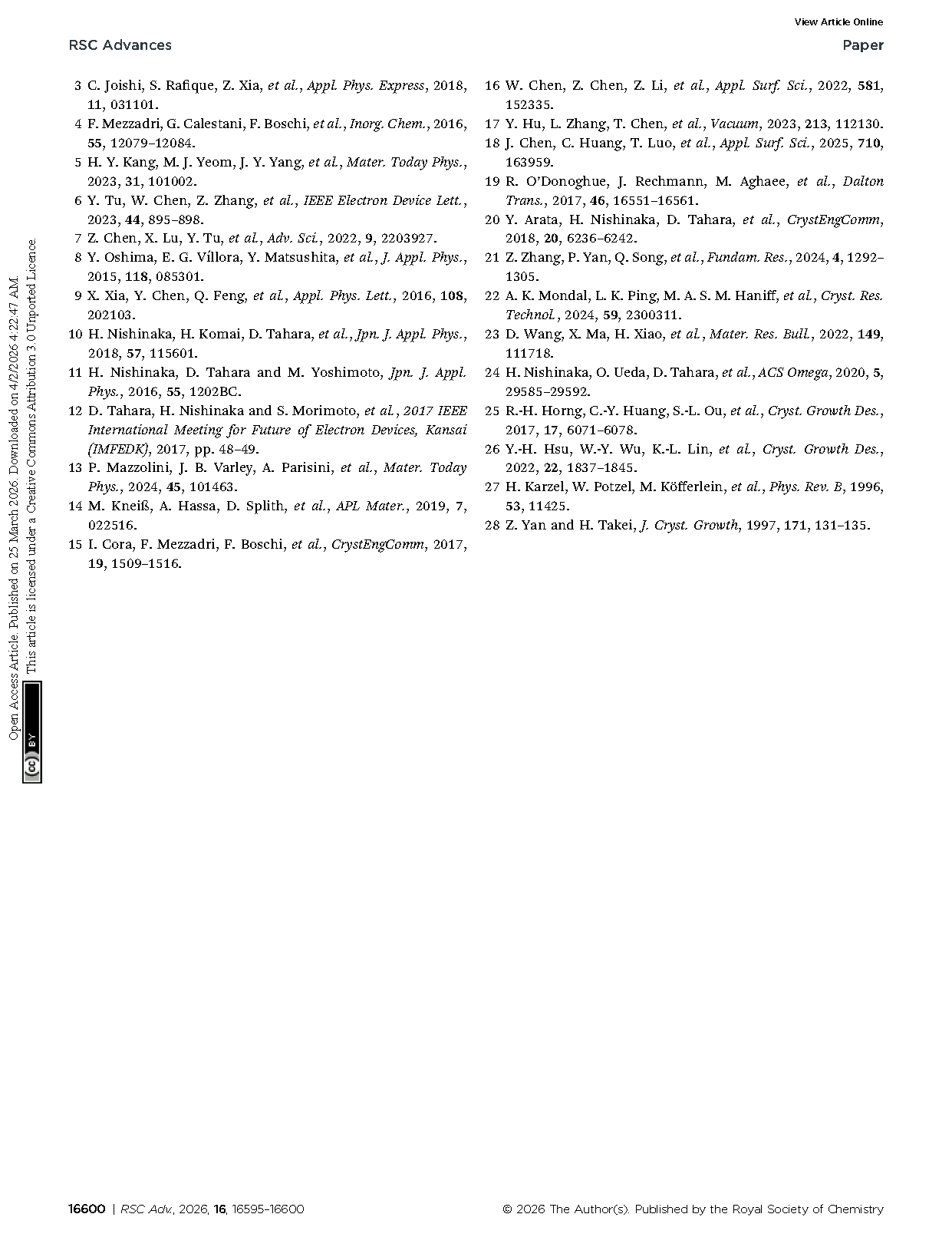

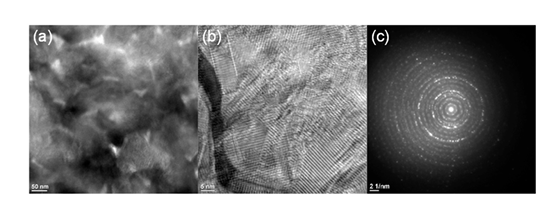

图 2 (a) κ‑Ga₂O₃/GZO/Si (100) 结构的截面 TEM 图像;(b) GZO/Si 界面、(c) ZnGa₂O₄ 中间层、(d) κ‑Ga₂O₃ 薄膜的高分辨 TEM 图像;(e) κ‑Ga₂O₃ 层的截面选区电子衍射 (SAED) 图谱。

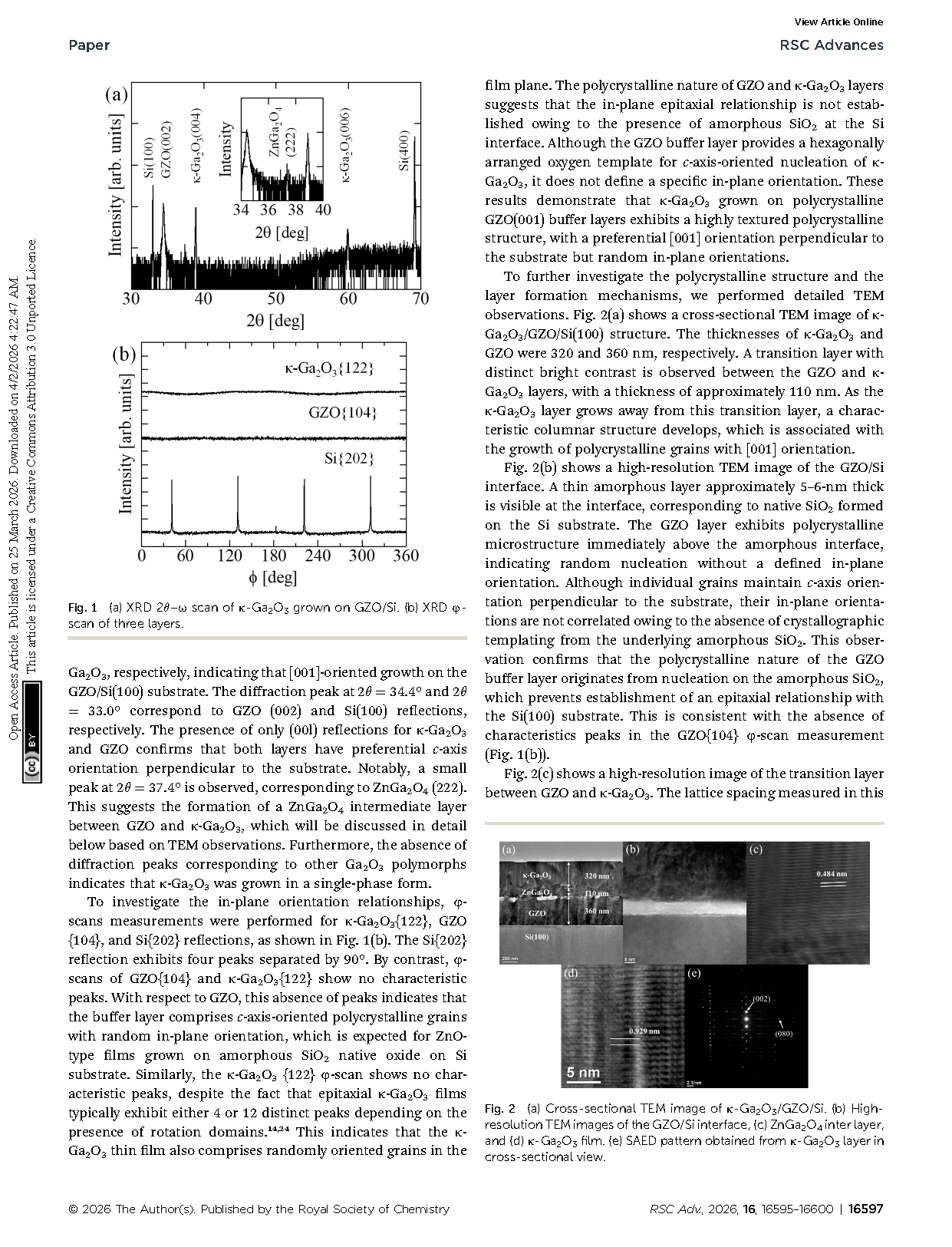

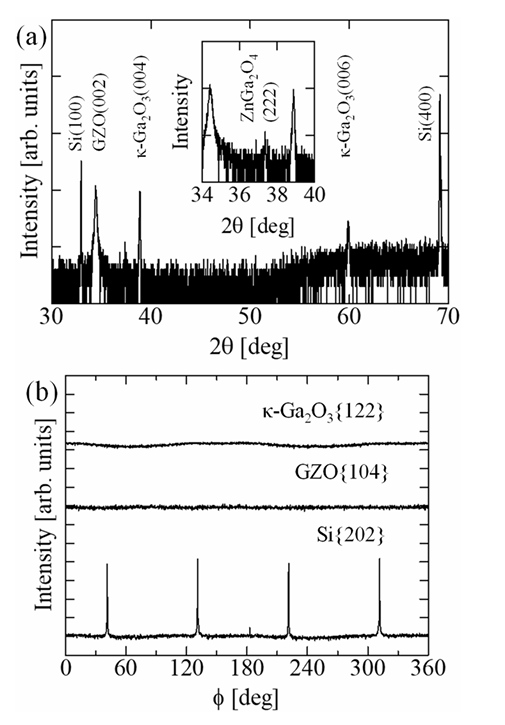

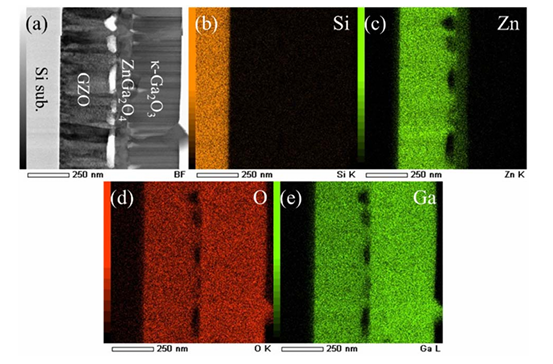

图 3 (a) κ‑Ga₂O₃/GZO/Si 的 STEM 图像;(b)–(e) Si、Zn、O、Ga 元素的面分布图谱。

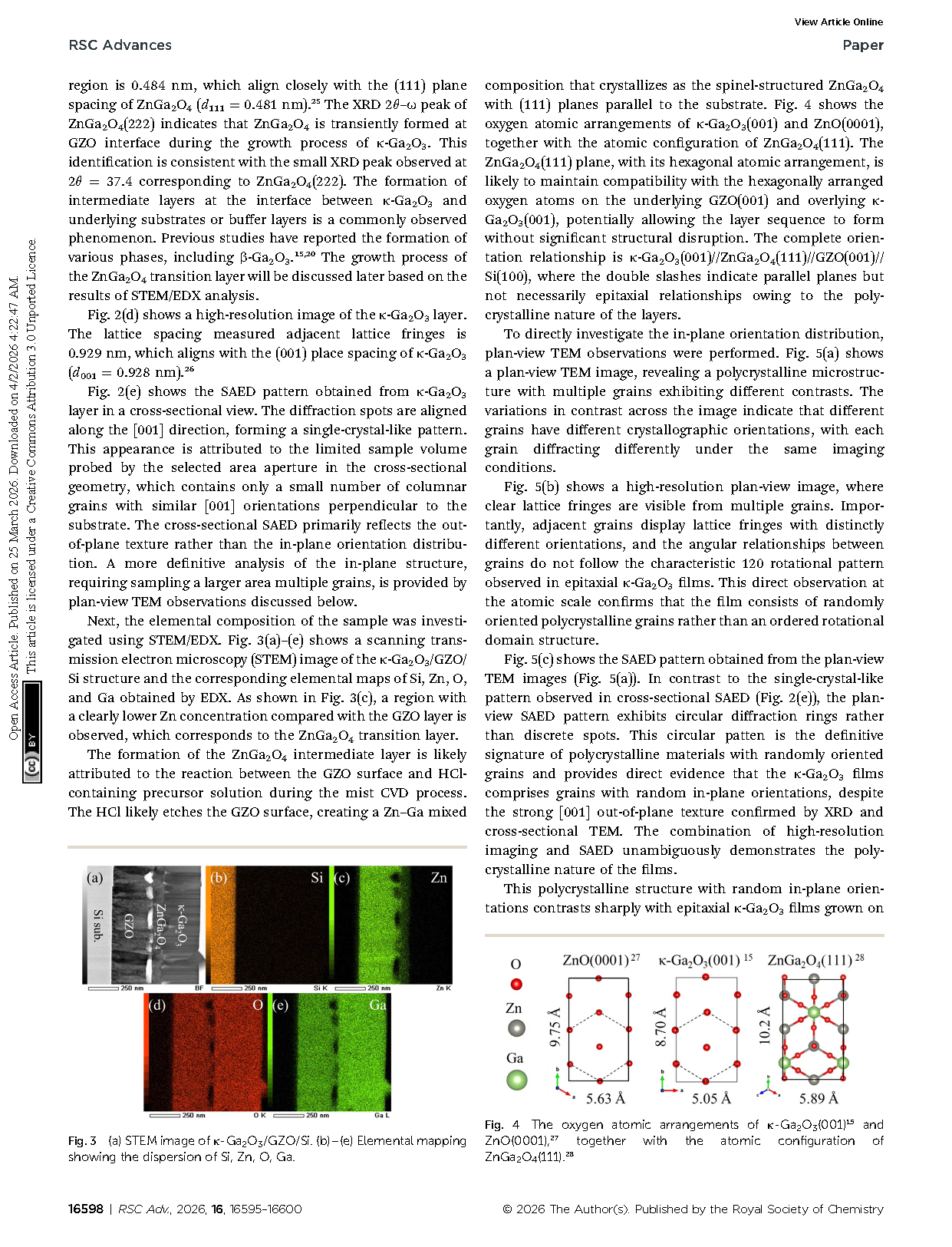

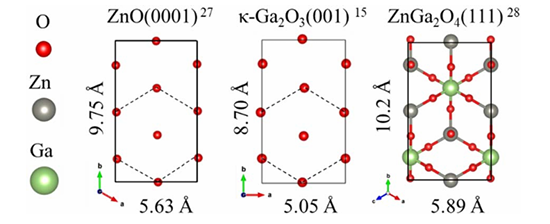

图 4 κ‑Ga₂O₃(001) 与 ZnO (0001) 的氧原子排列,以及 ZnGa₂O₄(111) 的原子构型。

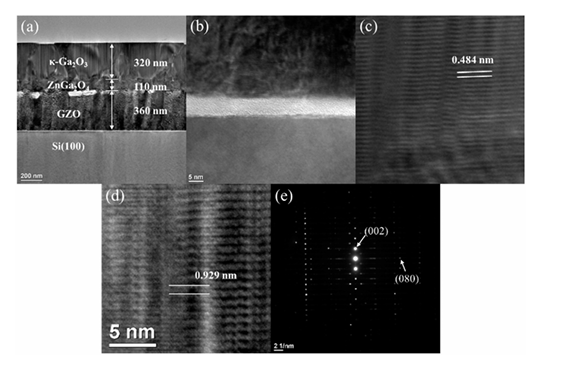

图 5 (a) κ‑Ga₂O₃ 薄膜的平面 TEM 图像;(b) κ‑Ga₂O₃ 的平面高分辨 TEM 图像;(c) 平面 TEM 对应的选区电子衍射 (SAED) 图谱。

DOI:

doi.org/10.1039/D6RA00464D